1. 准备工作

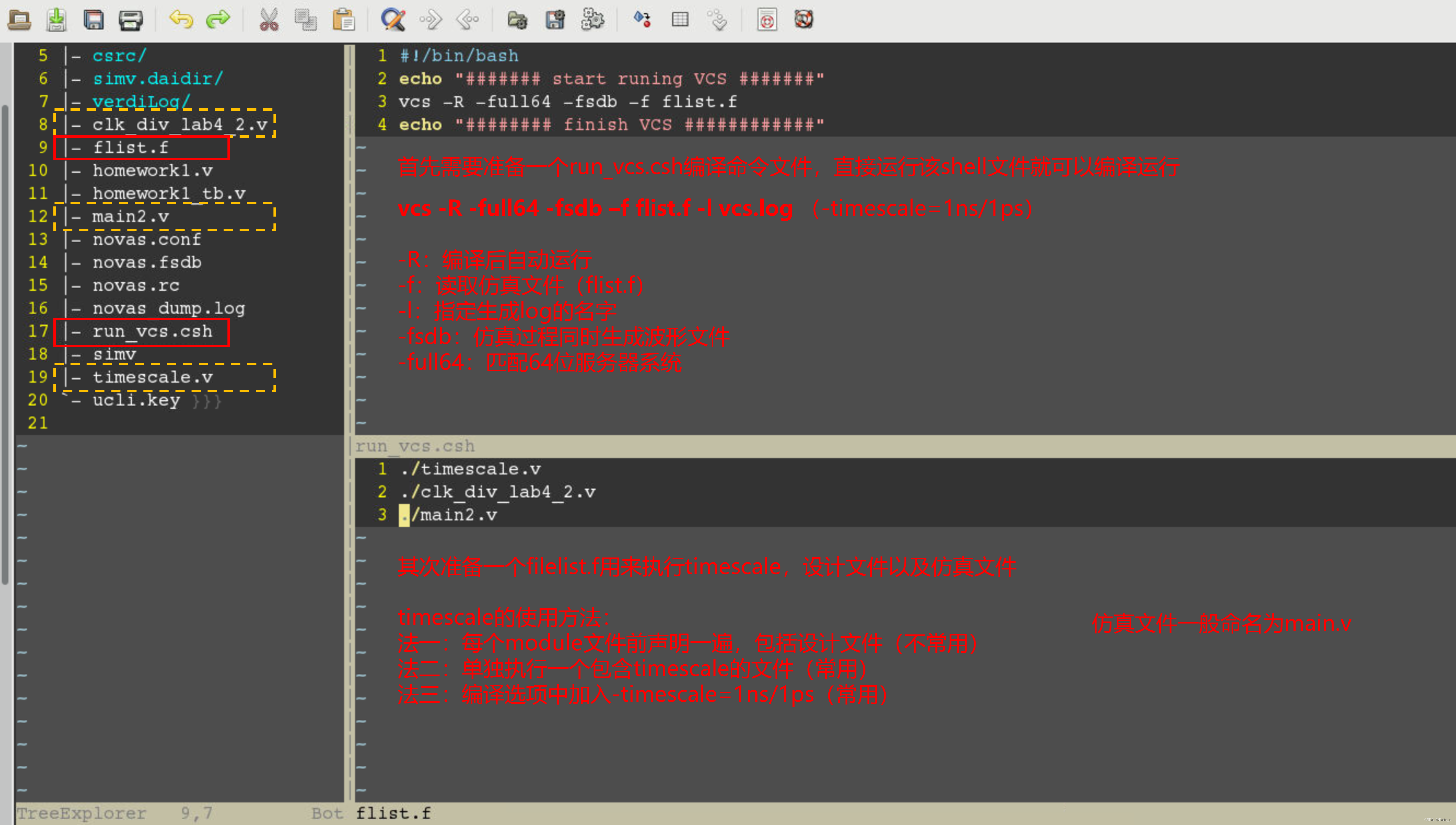

1. 写有vcs编译命令的run_vcs.csh的shell脚本

2. 装有timescale,设计文件以及仿真文件的flish.f(filelist文件,用于VCS直接读取)

vcs -R -full64 -fsdb -f flist.f -l test.log

2. 写代码(重点了解代码规范)

2.1 设计要求

设计一个分频器并写一个测试环境验证它。

要求:设计一共有一个输入,三个输出

输入为时钟频率为100M的信号

输出为三个时钟频率分别是50MHz,10MHz,1MHz

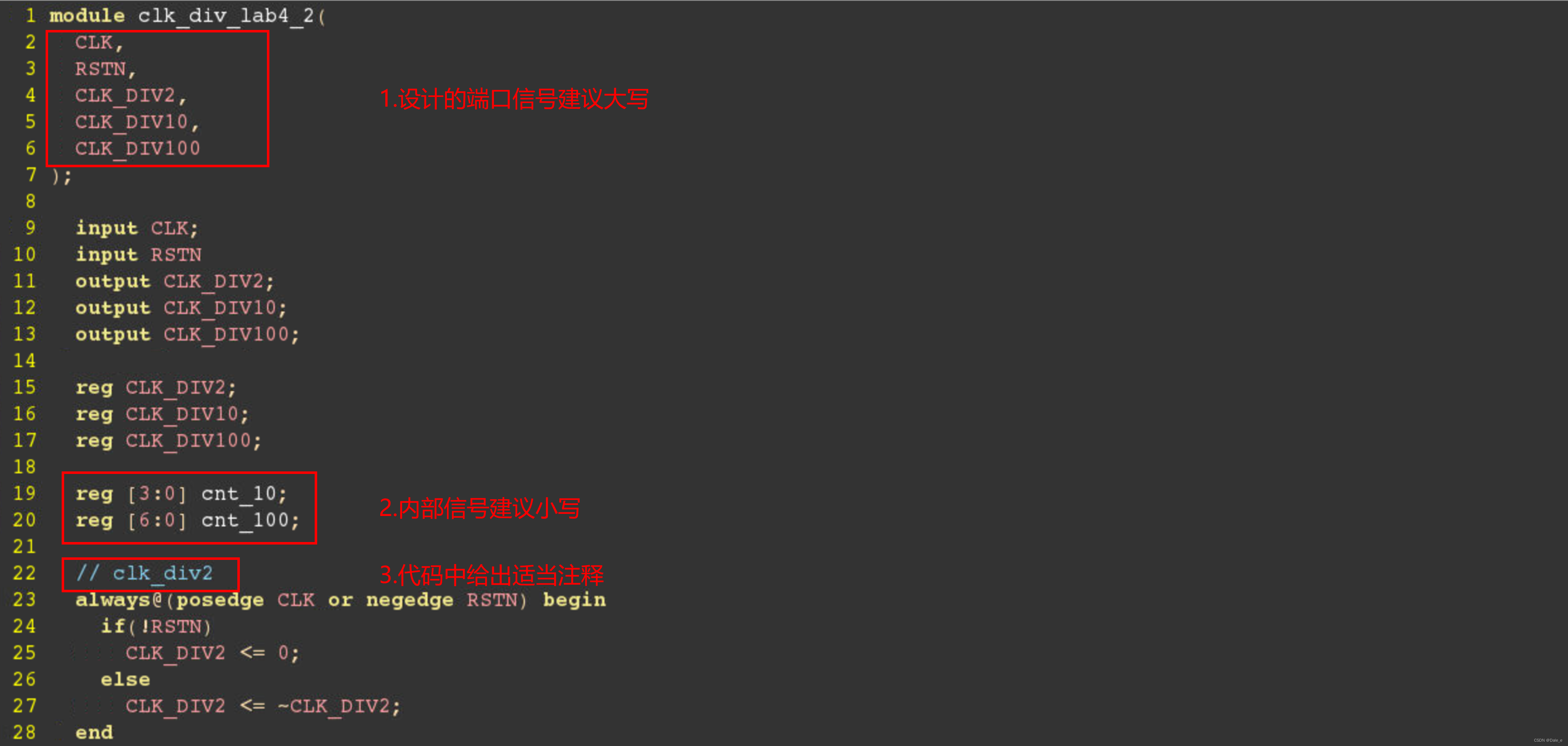

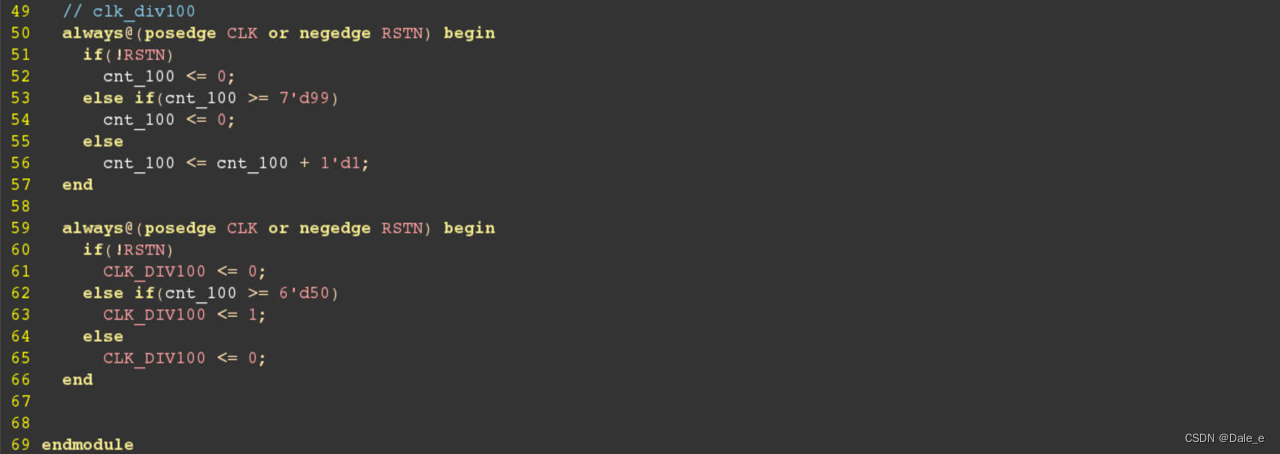

2.2 设计代码

1.设计端口信号建议大写

2.内部信号建议小写

3.代码中给出适当注释

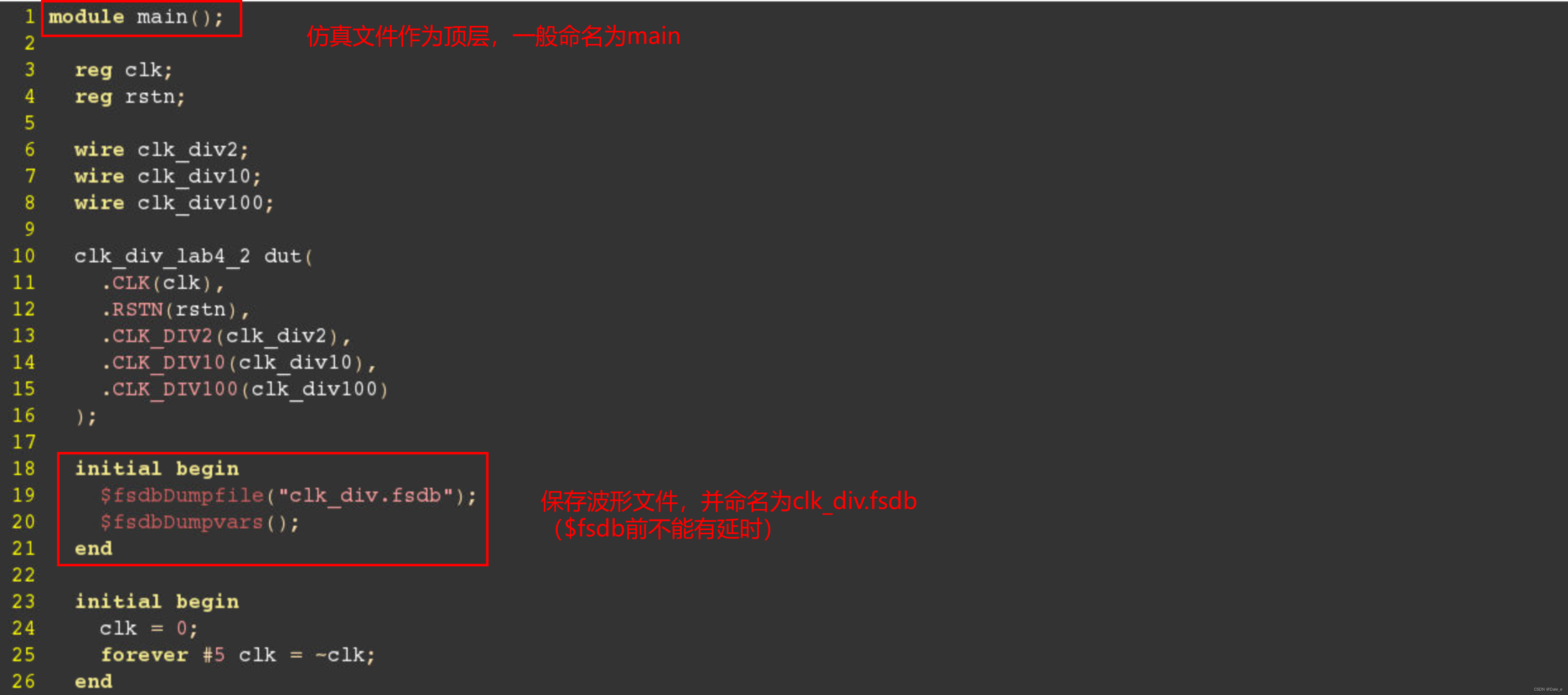

2.3 仿真代码

1.需要一个单独的initial块来保存波形文件

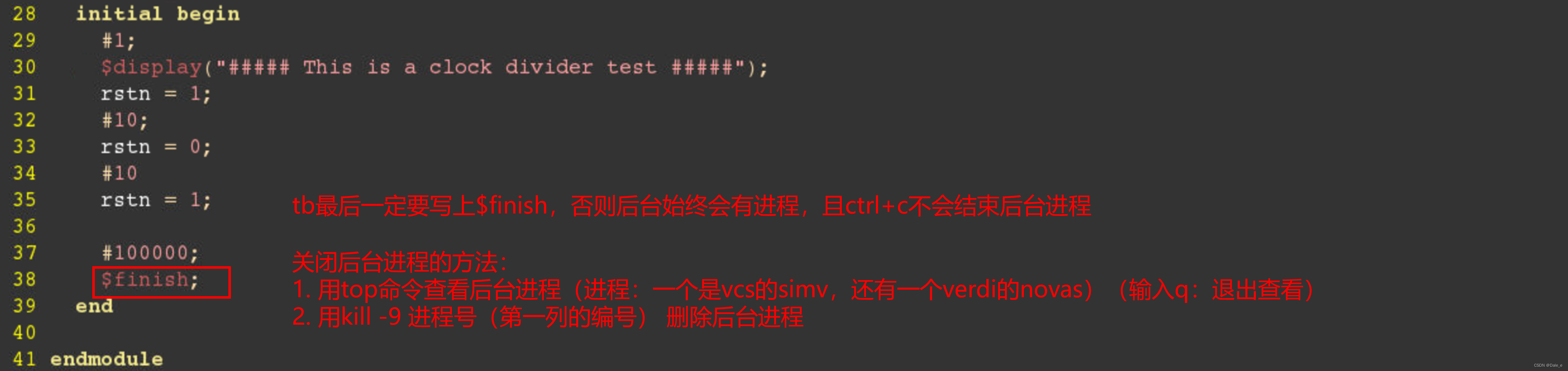

2.仿真最后一定要加上$finish

3. 使用verdi跑仿真

3.1 verdi启动命令

verdi -f flist.f -ssf clk_div.fsdb (-sswr file.rc)// -f flist.f 读取flist中的设计及仿真文件

// -ssf clk_div.fsdb 打开verdi的同时打开clk_div的波形窗口

// -sswr file.rc 打开波形窗口的同时打开保存过的某些信号的波形4. verdi相关操作

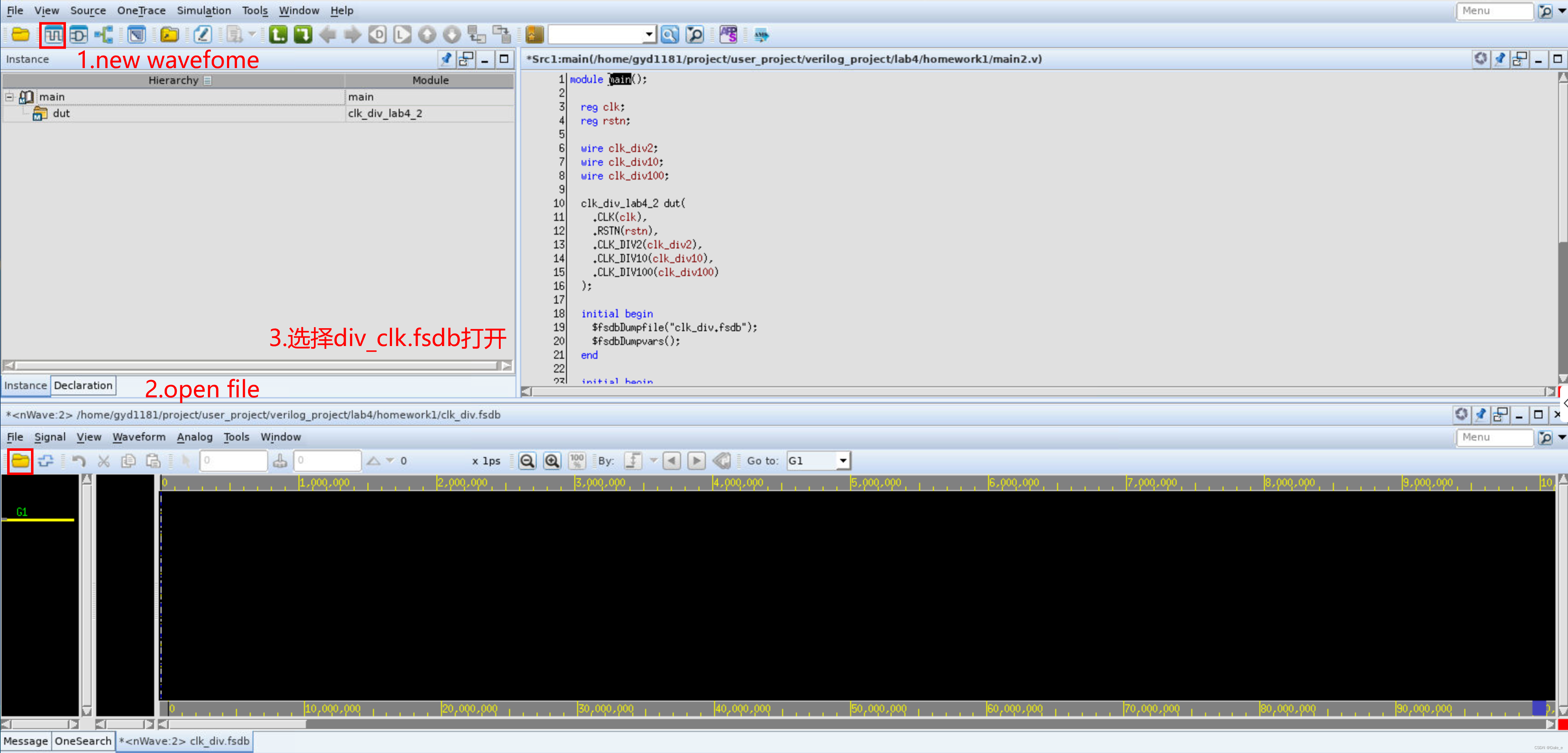

4.1 打开verdi中的波形

方法一:new wavefome图标,open file,打开test.fsdb文件

方法二:verdi -f flist.f -ssf clk_div.fsdb

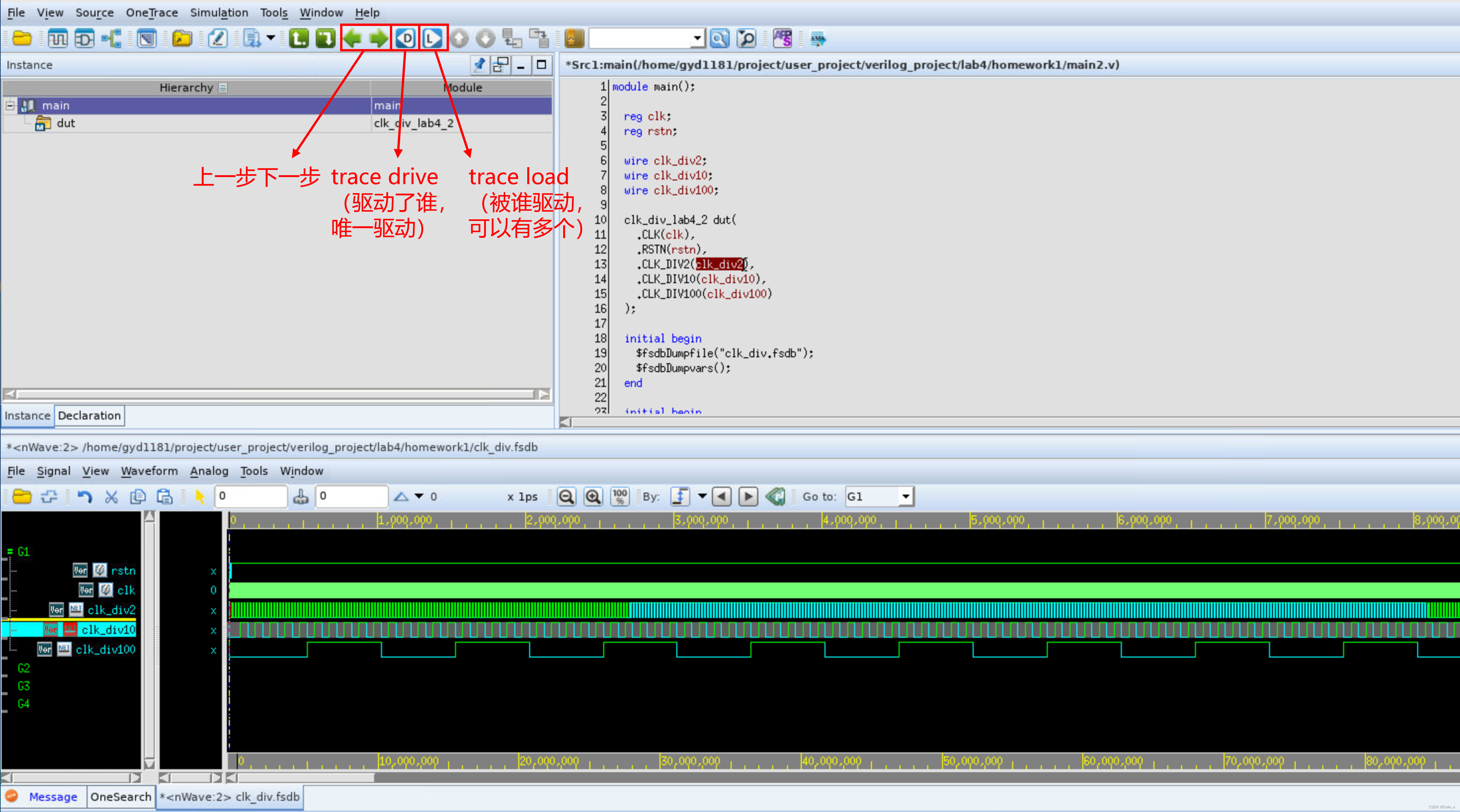

使用verdi -f -flist.f -ssf clk_div.fsdb命令打开后的窗口如下:

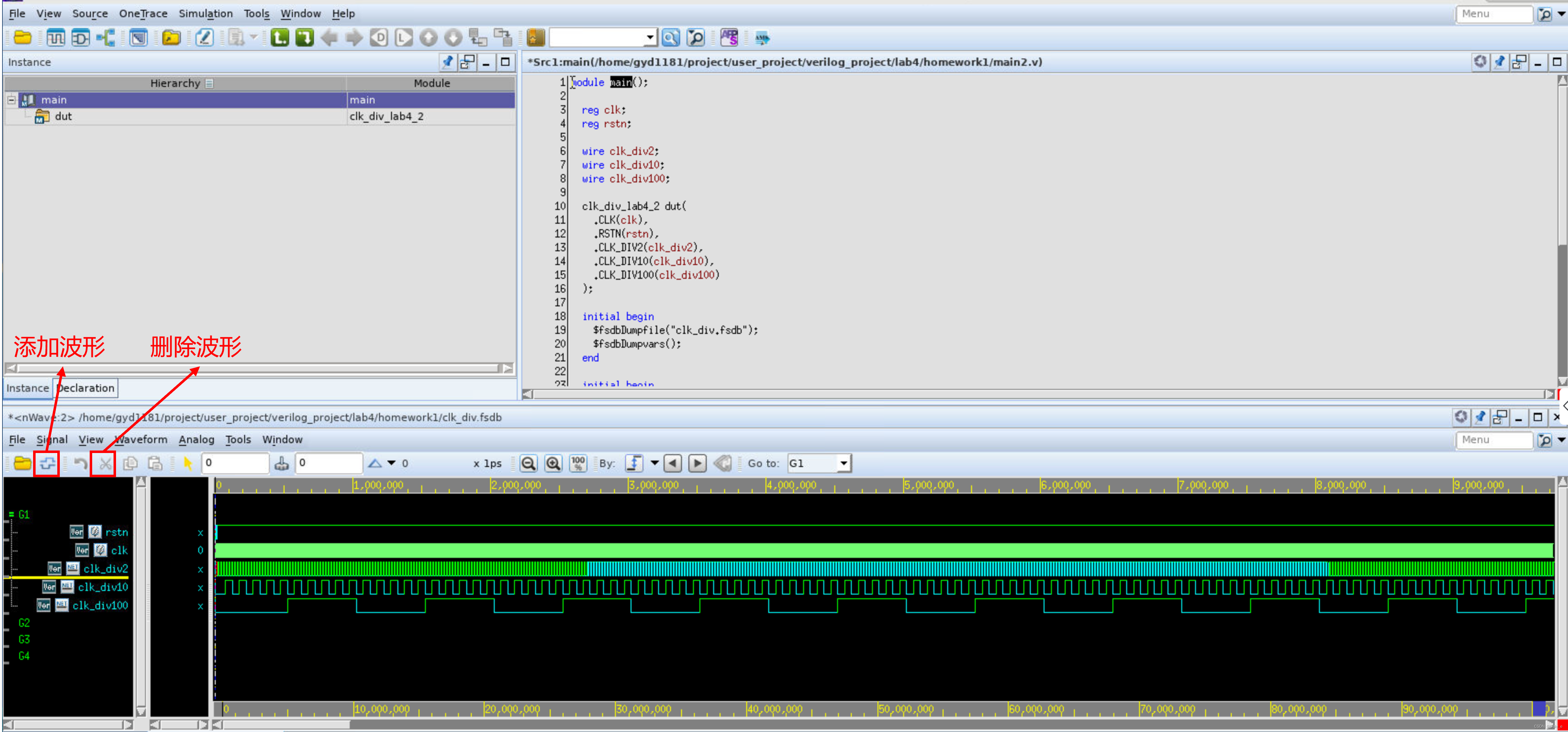

4.2 将信号添加到波形窗口

方法一:用鼠标中建直接把信号拖进波形窗口

方法二:选中一个信号,按ctrl+w(ctrl+w也是关闭网页的快捷键,有冲突)

方法三:点get signals图标

删除信号:delete or 右键,选剪刀图标

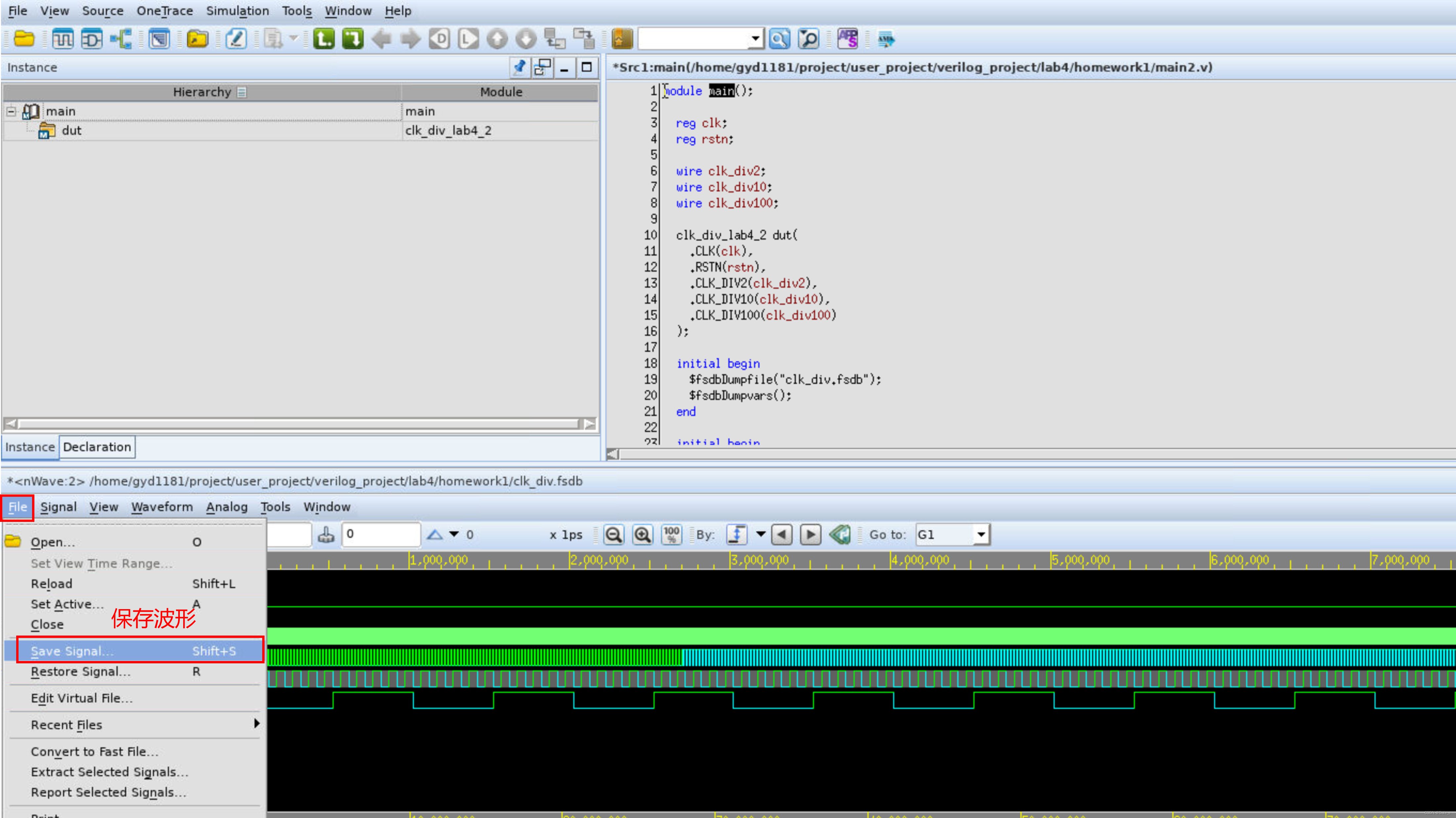

4.3 保存波形

保存波形:file—save signal :保存为.rc文件。

4.4 debug

法一:点击有问题的信号,查看谁驱动力该信号,前进后退箭头可以查看上一次和下一次

法二:双击有问题的波形处,代码会跳到驱动该信号的地方

4.5 更新代码

在gvim上修改好代码之后重新编译,编译通过后回到verdi中输入shift+L即可。