4位数值比较器电路

描述

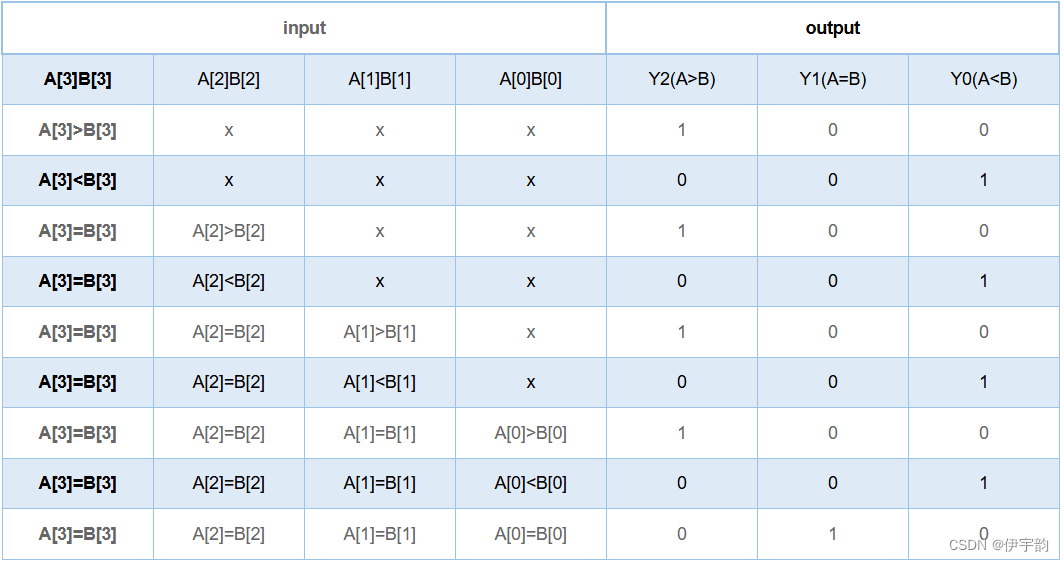

某4位数值比较器的功能表如下。

请用Verilog语言采用门级描述方式,实现此4位数值比较器

输入描述:

input [3:0] A ,

input [3:0] B

输出描述:

output wire Y2 , //A>B

output wire Y1 , //A=B

output wire Y0 //A<B

分析:

这里要注意题目的“门级描述方式”,所以我们只能使用基本门电路:&,|,!,^,^~。

门级描述,无非就是将<,>,==三个符号用门级电路来表示,然后根据行为级描述进行替换。

a == b --> ~(a^b)

a > b --> (a^b)&a

a < b --> (a^b)&b

行为级描述就是从最高位依次比较。

对于Y1; A = B 即

A[3] = B[3], A[2] = B[2], A[1] = B[1], A[0] = B[0],

如何描述呢?(^异或,相同为0,不同为1)

即 :

assign Y1 = ~(A[0]^B[0]) & ~(A[1]^B[1]) & ~(A[2]^B[2]) & ~(A[3]^B[3]);所以这道题的解题代码为:

`timescale 1ns/1nsmodule comparator_4(input [3:0] A ,input [3:0] B ,output wire Y2 , //A>Boutput wire Y1 , //A=Boutput wire Y0 //A<B

);assign Y1 = ~(A[0]^B[0]) & ~(A[1]^B[1]) & ~(A[2]^B[2]) & ~(A[3]^B[3]);assign Y2 = ((A[3]^B[3])&A[3]) | ~(A[3]^B[3]) & ((A[2]^B[2])&A[2])| ~(A[3]^B[3]) & ~(A[2]^B[2]) & ((A[1]^B[1])&A[1])| ~(A[3]^B[3]) & ~(A[2]^B[2]) & ~(A[1]^B[1] )& ((A[0]^B[0])&A[0]);assign Y0 = ((A[3]^B[3])&B[3]) | ~(A[3]^B[3]) & ((A[2]^B[2])&B[2])| ~(A[3]^B[3]) & ~(A[2]^B[2]) & ((A[1]^B[1])&B[1])| ~(A[3]^B[3]) & ~(A[2]^B[2]) & ~(A[1]^B[1] )& ((A[0]^B[0])&B[0]);

endmodule