LVDS(Low Voltage Differential Signaling,即 低电压差分信号 )

接口又称 RS-644 总线接口,是20世纪90年代才提出的一种 数据传输 和接口技术。 LVDS接口是美国NS美国国家半导体公司为克服以 TTL电平 方式传输宽带高码率数据时功耗大,电磁干扰大等缺点而研制的一种数字视频信号传输方式

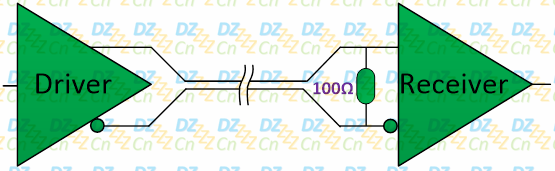

LVDS 驱动器级在一个始终开启的 3.5 mA (典型值)电流源环境中运行(请参见图 1)。只需通过差分对导体以不同方向重新分配电流,便可形成总线上的逻辑 1 和 0。这种消除开关噪声和 EMI 的“始终开启”特性正是降低 ADC 性能的主要原因。

LVDS 驱动器和接收机

由于专为点对点信号传输而设计,LVDS 使用的是一种简单的端接方案。安装在接收机输入端的单个 100-ohm 电阻端接差分对,从而消除了反射。

由于高阻抗接收机输入,驱动器电流源的全部电流流经端接电阻,从而产生了一个 350 mV 额定值的低、差分总线电压。该电压在 1.2 V 共模电位左右摆动,其为典型驱动器输出失调电压(请参见图 2)

LVDS 总线电压电平

相比单端方案,差分信号传输还有另一个 LVDS 好处,因为它不易受到共模噪声的影响,并且产生更少的电磁干扰 (EMI)。

由于接收机只响应差分电压,因此同邻近信号线迹耦合的噪声被接收机视作共模调制,从而被拒绝。另外,由于两个差分对导体传导电流相等但极性相反,因此它们的磁场基本互相抵消,从而实现 EMI 最小化。

根据数据速率的不同,标准 LVDS IC 可以驱动长达 10 米的距离。然而,不应强制高性能 ADC 驱动这一距离。取而代之的是,建议使用两英尺以内的短输出线迹长度,以防止邻近电路的噪声耦合到 ADC 输出端,因为其可能会反馈耦合至 ADC 模拟输入端。

尽管低功耗、低 EMI 和高噪声抗扰度使得 LVDS 成为高速数据转换器的接口选择,但是必须运用精心的布局技术,以避免阻抗不连续和信号时延差,否则就抵消了上述 LVDS 的好处。

1.LVDS接口的工作原理

LVDS接口采用差分信号传输方式,即每个信号线都由一对相互反向的信号传输线组成。其中,一根线传输正向电压信号,另一根线传输反向电压信号。这种差分传输方式可以有效地降低电磁辐射和抑制共模噪声,提高信号传输的可靠性和稳定性。

LVDS接口的工作原理可以简单描述为以下几个步骤:

-

发送端将输入的数字信号转换为差分信号:将输入信号分别与参考电平进行比较,并产生相应的差分信号。

-

差分信号经过发送器被驱动到信号线上:发送器会将差分信号转换为电流输出,并通过一对相互反向的传输线传输到接收端。

-

接收端将差分信号恢复为数字信号:接收器对接收到的差分信号进行放大和恢复,使其能够被正确解读为数字信号。

2.LVDS接口技术特点

LVDS接口具有以下几个技术特点:

-

高速传输能力:LVDS接口的传输速率通常在100Mbps到3.125Gbps之间,能够满足高速数据传输的需求。

-

低功耗:由于LVDS接口采用差分信号传输方式,相对于单端传输方式能够有效降低功耗。

-

抗干扰性好:差分传输方式可以抵消共模噪声和电磁辐射干扰,提供更可靠的信号传输质量。

-

线缆成本低:LVDS接口使用普通铜线材料进行传输,相对于光纤等其他传输介质,成本较低。

-

驱动能力强:LVDS接口可以驱动长距离的信号传输,最大传输距离可达数十米。

3.LVDS接口的应用模式

LVDS接口广泛应用于各种领域,包括但不限于以下几个方面:

-

显示器接口:LVDS接口常用于液晶显示器(LCD)的数据传输,可以实现高刷新率和高分辨率的显示效果。

-

通信系统:LVDS接口可以用于高速通信设备中,如路由器、交换机等网络设备的数据传输。

-

工业自动化:LVDS接口适用于工业自动化领域,可以实现高速数据传输和可靠的控制信号传输。

-

汽车电子:LVDS接口在汽车电子中起到重要作用,例如用于汽车仪表板上的显示屏传输图像数据。

总结起来,LVDS接口通过差分信号传输方式,具有高速传输能力、低功耗、抗干扰性好等技术特点。它在各个领域都有广泛的应用,并且不断发展壮大。随着技术的不断进步,LVDS接口也在不断演化和改进,以满足更高的传输速率和更广泛的应用需求。

未来的LVDS接口可能会有以下发展方向:

-

更高的传输速率:随着数据传输需求的增加,LVDS接口将不断提高传输速率,以满足更高的带宽要求。这可能涉及到技术上的创新和改进,例如引入多通道传输、调制解调技术等。

-

更低的功耗:随着节能环保意识的提高,LVDS接口也会朝着更低功耗的方向发展。这可能包括采用更低的供电电压、优化电路设计和降低功耗的技术措施。

-

高集成度:为了满足小型化和集成化的需求,未来的LVDS接口可能会趋向于更高的集成度,通过减少组件数量和简化接口结构,实现更紧凑和便捷的设计。

-

更广泛的应用领域:随着LVDS接口技术的不断发展,它有望进一步扩展到更多的应用领域。例如,LVDS接口可以应用于医疗设备、航空航天、军事领域等,为这些领域提供高速可靠的数据传输解决方案。

LVDS 两种接口标准比较这两种接口标准的区别在于:

每对低压差分信号上传输的 R、G、B 三色的位数和 HS、VS、DE 位置不同。

1. 8bit 液晶屏需要 4 对差分对传输 R、G、B 三色和 HS、VS、DE控制信号

(1)对应到 VESA接口标准

0+/-:RO,R1,R2,R3,R4,R5,G0

1+/:G1,G2,G3,G4,G5,B0,B1

2+1-:B2,B3,B4,B5,HS,VS, DE

3+1-:R6,R7,G6,G7,B6,B7,0

(2)对应到 JEIDA接口标准

0+/-:R2,R3,R4,R5,R6,R7,G2

1+/-:G3,G4,G5,G6,G7,B2,B3

2+/-:B4,B5,B6,B7, HS, VS, DE

3+/-:RO,R1,GO,G1,B0,B1,0

2. 10bit 液晶屏需要5 对差分对传输 R、G、B 三色和 HS、VS、DE控制信号

(1)对应到 VESA接口标准

0+/-:RO,R1,R2,R3,R4,R5,GO

1+/-:G1,G2,G3,G4,G5,B0,B1

2+/-:B2,B3,B4,B5,HS,VS, DE

3+/-:R6,R7,G6,G7,B6,B7,0

4+/-:R8,R9,G8,G9,B8,B9,0

(2)对应到 JEIDA接口标准

0+/-:R4,R5,R6,R7,R8,R9,G4

1+/-:G5,G6,G7,G8,G9,B4,B5

2+/-:B6,B7,B8,B9, HS,VS, DE

3+/-:R2,R3,G2,G3,B2,B3,0

4+/:RO,R1,GO,G1,B0,B1,0

单路和双路 LVDS 信号

单路就是只有一路 R、G、B 三色和 HS、VS、DE控制信号;

双路就是有两路 R、G、B 三色和 HS、VS、DE控制信号。

为什么需要双路 LVDS 信号?

如1920 *1080P 的液晶显示屏,屏幕刷新率 60HZ,如果使用单路LVDS信号,那么需要的像素时钟为 1920*1080*60=124416000,约为124MHZ.而实际很少会采用频率这么高的晶振,并且 LVDS 的传输速率只能达到几百Mbps。如果再对屏幕像素尺寸和刷新率有更高要求,那需要的时钟频率会更高。

一个像素24bit,24*124M>2400 M,所需传输速率至少2400Mbps。bps是bit per second。

采用双路 LVDS 就是将显示界面分为奇像素点和偶像素点,在一个像素时钟周期内,完成对奇像素和偶像素两个像素点扫描赋值,那么所需要的时钟频率就大幅减小。

LVDS的发送器与接收器的基本结构如下图所示。它使用两根线(即差分信号线)来传输一个信号,并且使用恒流源(Current Source)驱动,即电流驱动型(而TTL、CMOS之类电平标准为电压驱动型)。

其中,驱动器(Driver)中的场效应管Q1、Q2、Q3、Q4(不一定是场效应管,因为LVDS技术规范主要侧重于LVDS接口的电气我、互连与线路端接,对于生产工艺、传输介质及供电电压无明确要求,也就是说,可以采用CMOS、GaAs或其它工艺实现,能抓到老鼠的黑猫白猫都是好猫)组成一个全桥开关电路,用来控制3.5mA恒流源的电流流动方向,接收器(Receiver)的同相与反相端之间并联了一个100欧姆的端接电阻,这样电流经过电阻即可产生电压,再经过接收器判断就形成了高低电平。

当Q2、Q3导通而Q1、Q4截止时,恒流源电流经Q3流向接收器,并向下穿过100欧姆端接电阻再返回至驱动端,最后经Q2到地(GND),3.5mA的电流在100欧姆电阻上产生350mV的压降,此时同相端电压高于反相端电压,输出为高电平“H”,如下图所示:

而当Q2、Q3截止而Q1、Q4导通时,恒流源电流经Q1向右流向接收器,并向上穿过100欧姆端接电阻再返回至驱动端,最后经Q4到地(GND),3.5mA的电流在100欧姆电阻上也产生350mV的压降,但此时同相端电压低于反相端电压,输出为高电平“L”,如下图所示:

通常我们将LVDS接收器与发送器简化成类似下图所示:

如下图所示

从LVDS结构原理可以看出,一对差分信号线只能够进行一个方向的数据传输,即单工通信(也称为点对点传输,point-to-point),但是我们常见的USB接口也只是使用一对差分信号线,为什么却可以双向传输呢?原因很简单,它是使用两对驱动器与接收器组合而成的,如下图所示:

这是一种半双工(half duplex)的配置结构,也就是说,在任意时刻差分信号线仍然只能是往一个方向传输数据,但可以分时进行双向数据传输,当驱动器1向接收器1发送数据时,驱动器2与接收器2相当于无效的,反之亦然。

当然,USB总线的实际结构要复杂得多,如下图所示(来自USB2.0规范,扯远了)

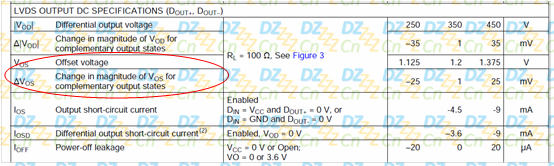

我们来看看如下图所示的LVDS驱动器电气参数(来自TI公司LVDS收发芯片SN65LVDS180数据手册)

上表中的VOD(Differential output voltage magnitude)即驱动器的差分输出电压幅度,也就是前述在端接电阻上产生的350mV压降,我们可以用下图所示(注意:是差模信号):

表中还有一个VOC(SS)(Steady-state common-mode output voltage)即稳态共模输出电压是个什么东西呢?我也不是很明白!咱们按图索骥找到数据手册中的Figure 3,如下图所示:

哦,原来是当驱动器输入数字信号(未转换成LVDS信号前)时,转换出来的LVDS信号电压对公共地的平均值,也称为VOS(Offset Voltage,),TI公司的其它数据手册有使用VOS如下图所示:(来自TI公司的LVDS收发芯片型号SN65LVDS049数据手册)

我们之前讲过,当使用LVDS电平标准传输高低电平时,接收端收到了+350mV或-350mV的压降只是差模信号,实际上还有一定的共模信号,它不影响接收器进行数据的判断。

当驱动器向接收器发送高电平“H”时,其等效图如下所示(注意:这个等效图仅适合传输线非常短的条件下):

当驱动器向接收器发送低电平“L”时,其等效图如下图所示

综合以上两种等效电路,我们有如下图所示的电平波形图:

换言之,当LVDS进行高低电平切换时,电流源的电流在换向的瞬间,端接电阻流过的电流为零,因此端接电阻两端的电压就是VOS(电阻两端电压相同,因此没有压降,也没有电流),如下图所示:

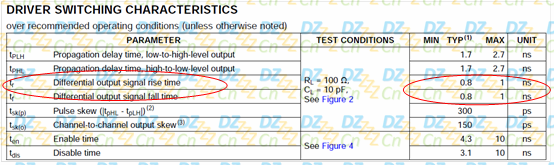

当然,这个电流换向转换瞬间非常短,通常只有几百皮秒,如下图所示:

接收器的输入电气参数如下图所示:

LVDS电平标准的噪声容限

从图中可以看到,LVDS电平标准的噪声容限约为1.075V(一般认为其噪声容限为 1V)这里我们只是根据TI数据手册画出电平标准图,没有做任何修改,不同厂家的信息可能略有不同