1. 引言

在现代电子技术中,微控制器(MCU)作为核心组件,广泛应用于各种电子系统中。随着电子设备向小型化、高性能化和高可靠性方向发展,MCU在复杂环境下的稳定性变得尤为重要。单粒子效应(Single Event Effect, SEE)是微电子器件在空间辐射环境中常见的故障模式之一,对MCU的正常运行构成严重威胁。本文以AS32S601型MCU为例,详细探讨其单粒子效应试验的数值计算与分析,旨在为相关研究和应用提供参考。

2. 单粒子效应概述

单粒子效应是指高能粒子(如质子、重离子等)在穿过半导体器件时,与晶格原子发生碰撞,产生大量电离电子-空穴对,从而引发器件内部电学性能的瞬态或永久性变化。根据效应的性质和表现形式,单粒子效应可以分为以下几种类型:

单粒子翻转(Single Event Upset, SEU):高能粒子撞击导致存储单元或触发器的状态发生瞬态改变,通常为非破坏性,可通过复位或重置恢复。

单粒子锁定(Single Event Latch-up, SEL):高能粒子撞击引发器件内部寄生双极型晶体管的导通,导致器件电流急剧增加,可能损坏器件。

单粒子烧毁(Single Event Burnout, SEB):高能粒子撞击导致器件内部局部过热,可能烧毁器件。

单粒子瞬态(Single Event Transient, SET):高能粒子撞击引发的瞬态电压或电流脉冲,可能影响电路的正常工作。

3. AS32S601型MCU简介

AS32S601型MCU是国科安芯研制的一款高性能32位RISC-V指令集微控制器,具有高安全、低失效、多IO、低成本等特点。其主要技术参数如下:

工作频率:高达180MHz

工作电压:2.7V~5.5V

休眠电流:≤200uA(可唤醒)

典型工作电流:≤50mA

存储容量:512KiB内部SRAM,512KiB D-Flash,2MiB P-Flash

封装类型:LQFP144

单粒子效应抗性:SEU≥75MeV·cm²/mg,SEL≥75MeV·cm²/mg

4. 单粒子效应试验方法

4.1 试验目的

本次试验旨在评估AS32S601型MCU在空间辐射环境中的抗单粒子效应能力,通过模拟高能粒子撞击,研究其在不同能量条件下的单粒子效应表现。

激光模拟单粒子效应技术原理解析

4.2 试验装置

试验采用皮秒脉冲激光单粒子效应试验装置,主要由以下设备组成:

皮秒脉冲激光器:产生高能激光脉冲,模拟高能粒子撞击。

光路调节和聚焦设备:将激光聚焦到芯片表面。

三维移动台:控制芯片在激光照射下的位置移动。

CCD摄像机:实时监测芯片表面和激光光斑的位置。

控制计算机:编程控制三维移动台的运动和激光的发射。

4.3 试验条件

试验地点:中关村B481脉冲激光单粒子效应实验室。

环境条件:温度24℃,湿度42%RH。

试验样品:AS32S601型MCU芯片,芯片尺寸为3959×3959μm²,工作电压5V,工作电流100mA。

4.4 试验方法

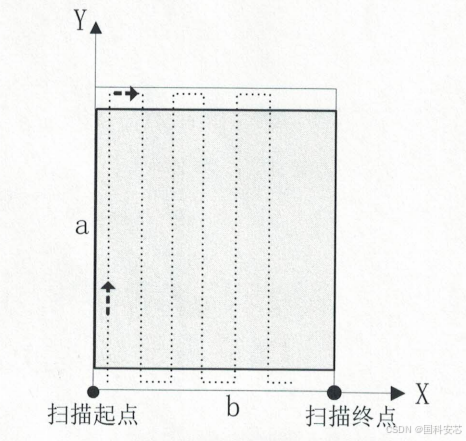

4.4.1 扫描方法

试验前将芯片固定于三维移动台上,设定扫描起点为芯片左下角。激光以1×10⁷cm⁻²的注量覆盖扫描芯片,扫描如图所示:

4.4.2 激光注量与能量

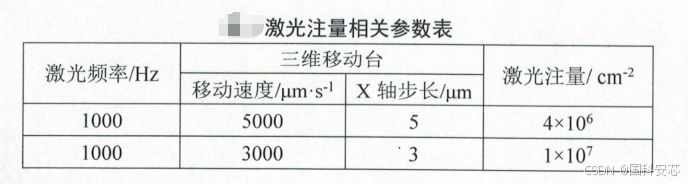

在本次试验中,激光注量设定为1×10⁷cm⁻²,对应的X轴和Y轴步长分别为5μm和3μm。具体参数如表1所示

4.4.3 激光能量与LET值关系

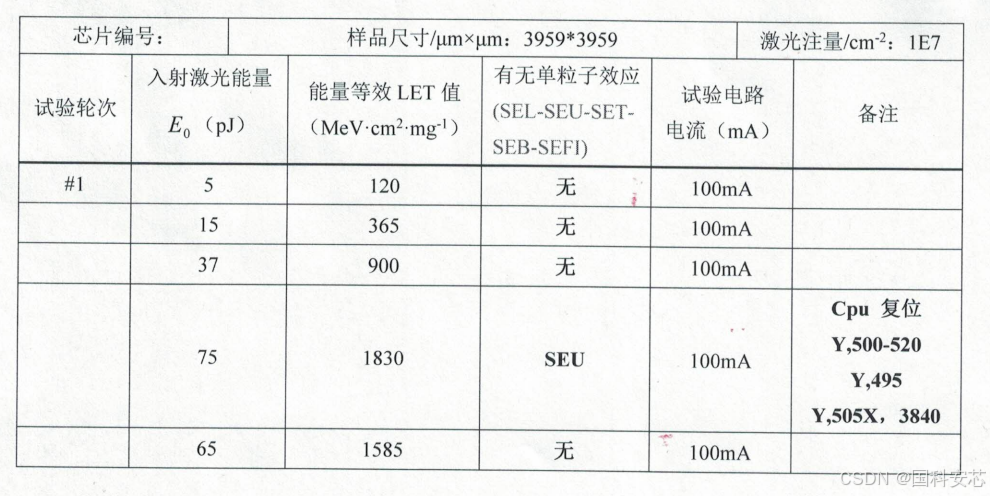

线性能量传输(LET)是指高能粒子在单位路径长度上沉积的能量。根据激光能量与重离子LET值对应关系计算得到扫描初始激光能量设定为120pJ(对应LET值为(5±1.25)MeV·cm²/mg),最高采用的能量为1830pJ(对应LET值为(75士18.75)MeV·cm²/mg)。如采用激光有效能量为对应 LET值=5MeV·cm²/mg时芯片不发生锁定,则增大激光能量(也即增大对应的LET值)。

4.4.4 单粒子效应判定

当芯片工作状态出现异常(超过正常工作电流的1.5倍),认为发生单粒子锁定效应(SEL)。发生单粒子效应时,手动给测试电路断电,关闭激光快门,停止扫描。

5. 数值计算与分析

5.1 试验结果

AS32S601型MCU在5V的工作条件下,利用激光能量为120pJ(对应LET值为5MeV·cm²/mg)开始进行全芯片扫描,未出现单粒子效应。当激光能量提升至1585pJ(对应LET值为75MeV·cm²/mg)时,监测到芯片发生单粒子翻转(SEU)现象。

5.2 结果分析

根据试验结果,AS32S601型MCU在低能量条件下表现出良好的抗单粒子效应能力。然而,在高能量条件下,芯片发生单粒子翻转,说明其在极端辐射环境下仍存在一定风险。这可能与芯片内部的存储单元或触发器的敏感性有关。

6. 结论

AS32S601型MCU在单粒子效应试验中表现出较好的抗单粒子效应能力。通过详细的数值计算与分析,本文揭示了其在不同能量条件下的单粒子效应表现,并提出了相应的改进建议。未来的研究将进一步优化芯片设计,提高其在复杂环境下的可靠性。