这里写目录标题

- 一、systemverilog的大部分新语法

- logic

- always_comb

- unique_case

- priority case

- always_ff

- typedef

- struct

- enum

- union

- interface

- 二、实现流水灯

- 三、全加器以及仿真

一、systemverilog的大部分新语法

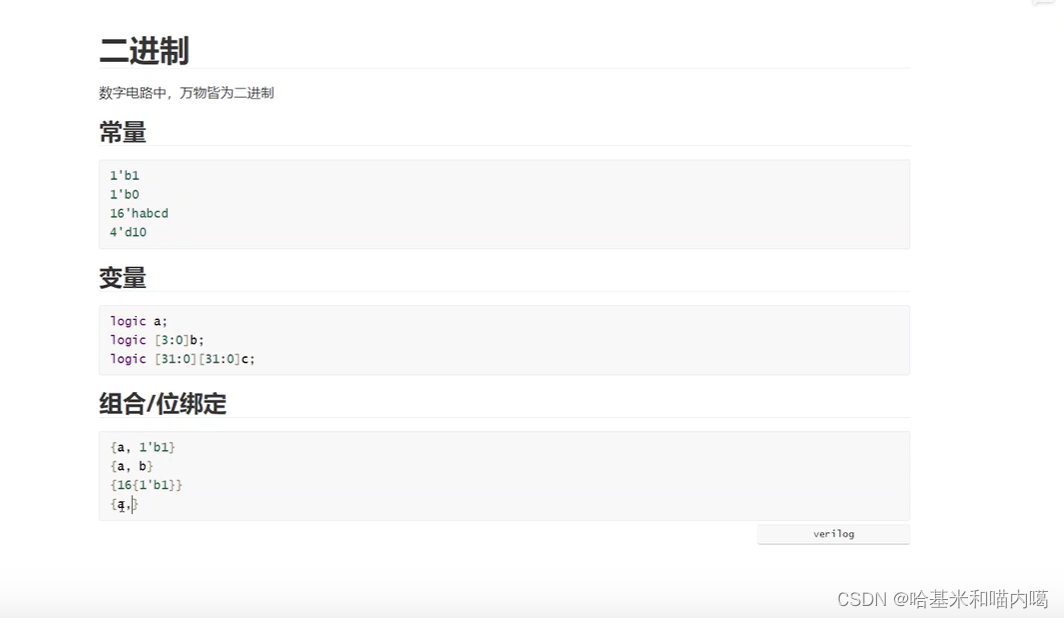

logic

always_comb

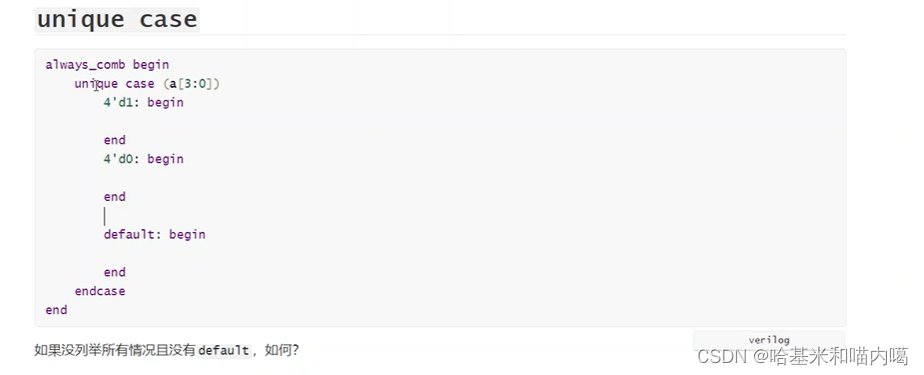

unique_case

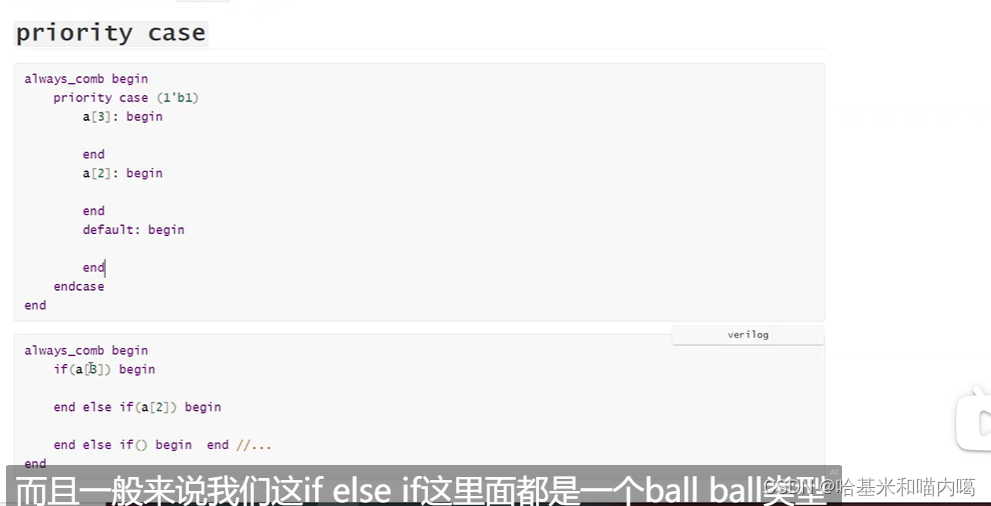

priority case

case中常量和变量互换位置

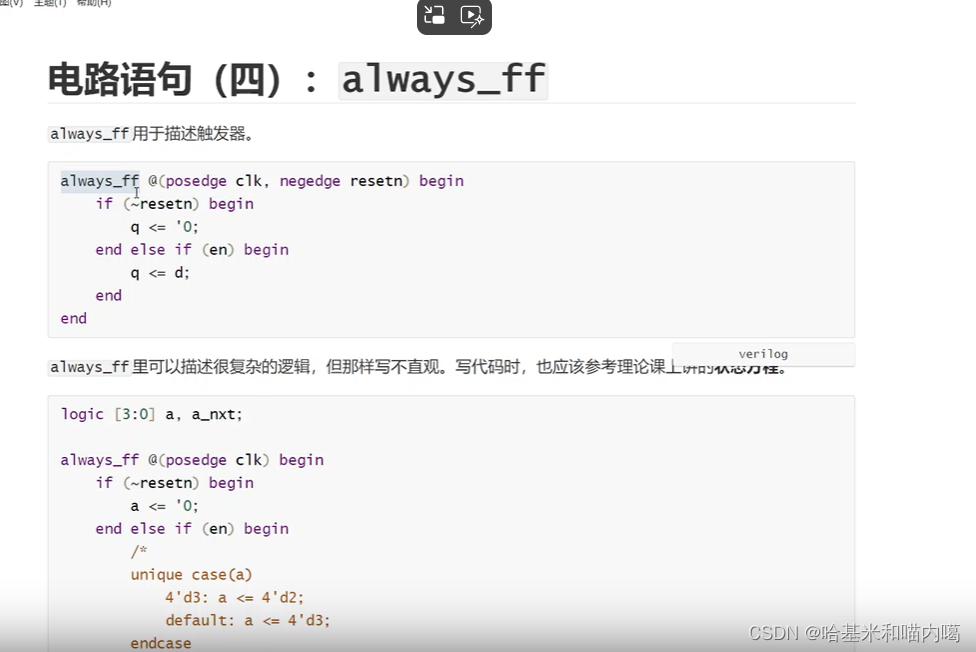

always_ff

typedef

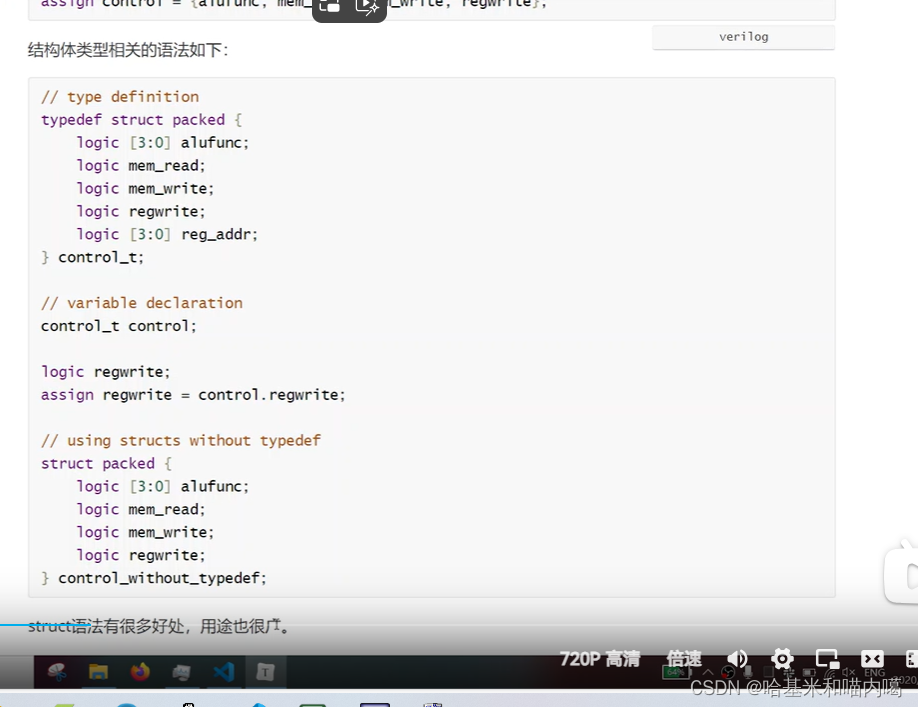

struct

enum

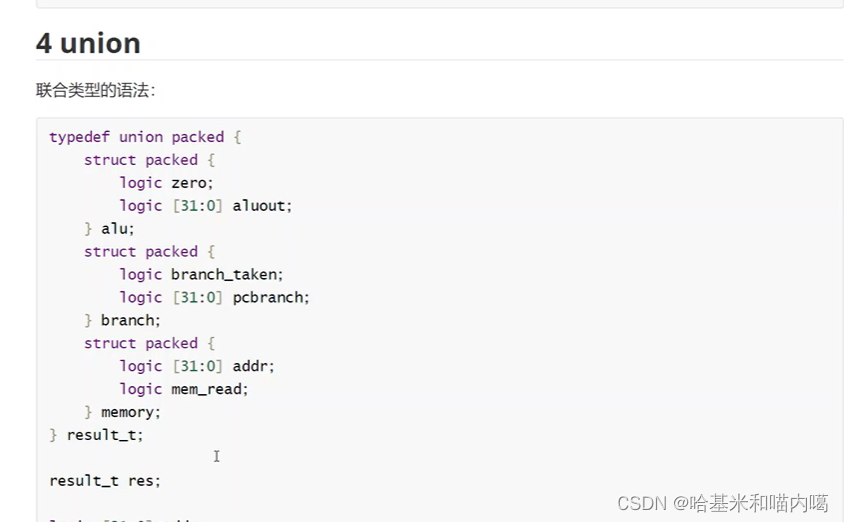

union

要求数据一样长

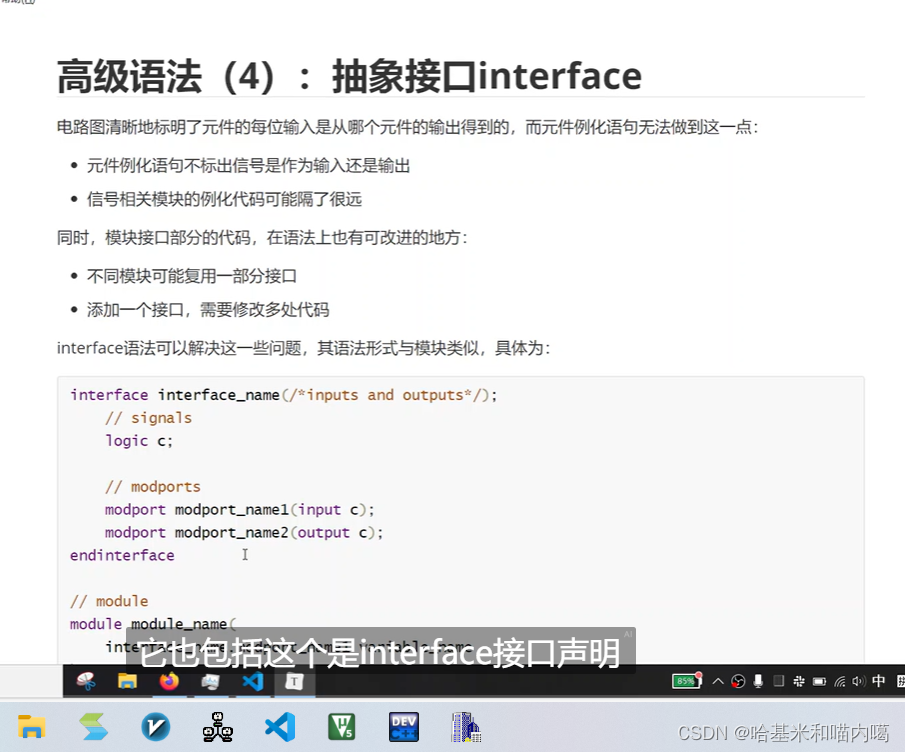

interface

二、实现流水灯

module ShiftRegister(input logic clk,input logic reset,output logic [7:0] leds

);logic [7:0] shift_reg;always_ff @(posedge clk or posedge reset) beginif (reset)shift_reg <= 8'b00000001;elseshift_reg <= {shift_reg[6:0], shift_reg[7]};endassign leds = shift_reg;endmodule

nios2_flow_led

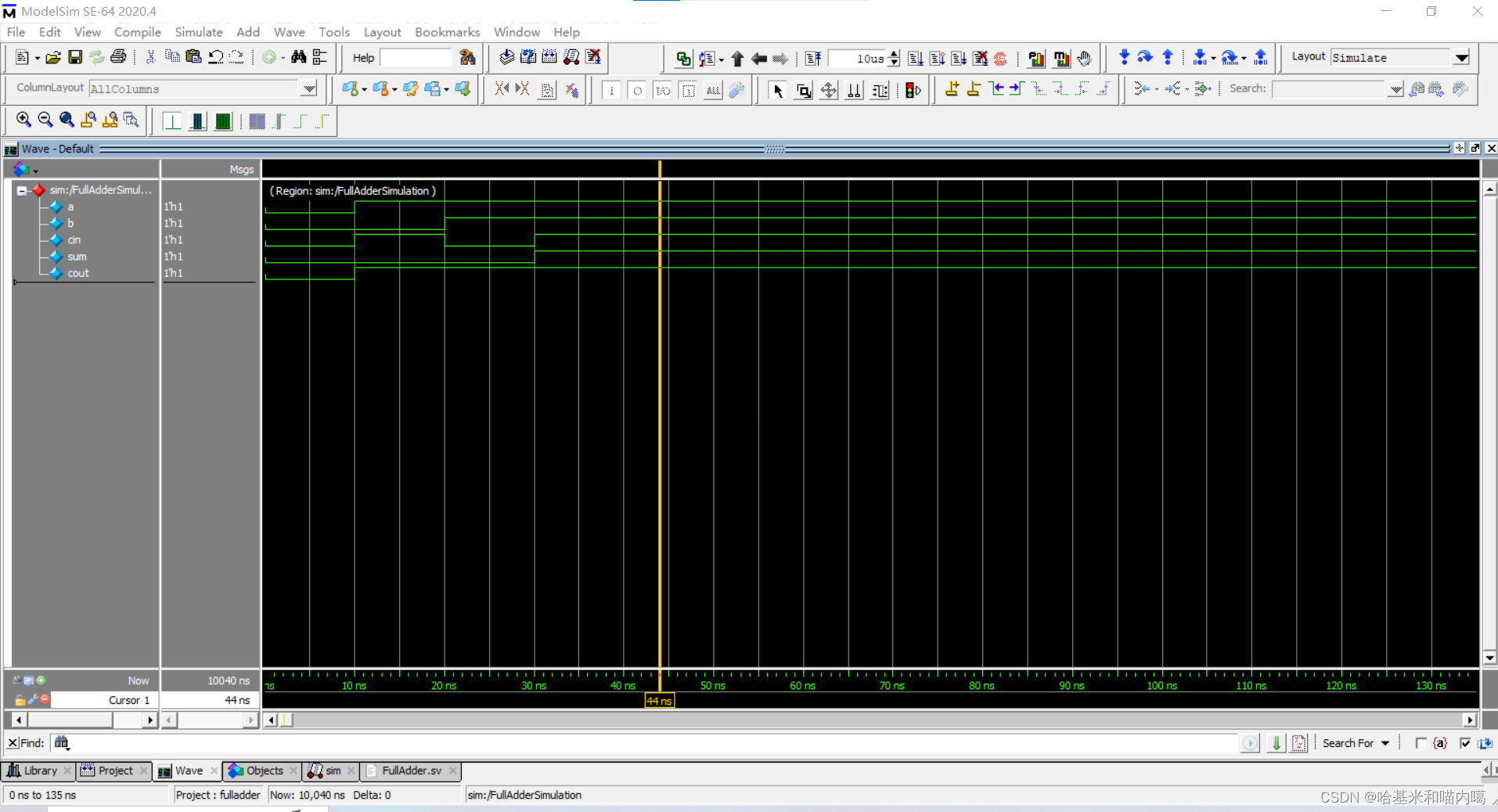

三、全加器以及仿真

module FullAdder(input logic a,input logic b,input logic cin,output logic sum,output logic cout

);assign sum = a ^ b ^ cin;assign cout = (a & b) | (cin & (a ^ b));

endmodulemodule FullAdderSimulation;logic a, b, cin, sum, cout;FullAdder dut (.a(a),.b(b),.cin(cin),.sum(sum),.cout(cout));initial begin$dumpfile("full_adder.vcd");$dumpvars(0, FullAdderSimulation);// Test case 1: a=0, b=0, cin=0a = 0; b = 0; cin = 0;#10;// Test case 2: a=1, b=0, cin=1a = 1; b = 0; cin = 1;#10;// Test case 3: a=1, b=1, cin=0a = 1; b = 1; cin = 0;#10;// Test case 4: a=1, b=1, cin=1a = 1; b = 1; cin = 1;#10;$finish;end

endmodule

https://www.bilibili.com/video/BV1XA41177of/