1. 内存硬件实现机制

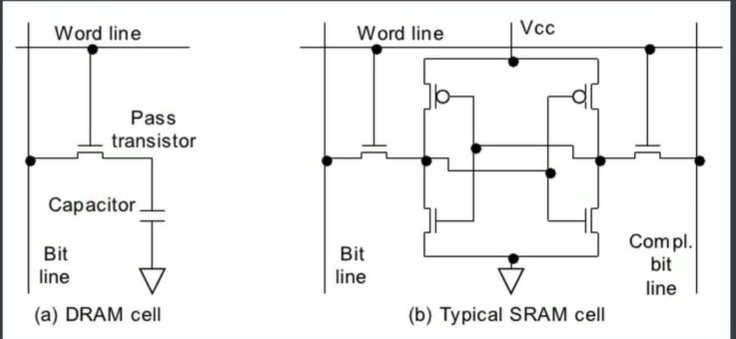

通过D触发器构建寄存器和内存的结构对比,这里主要先表达sram复杂,dram简单。

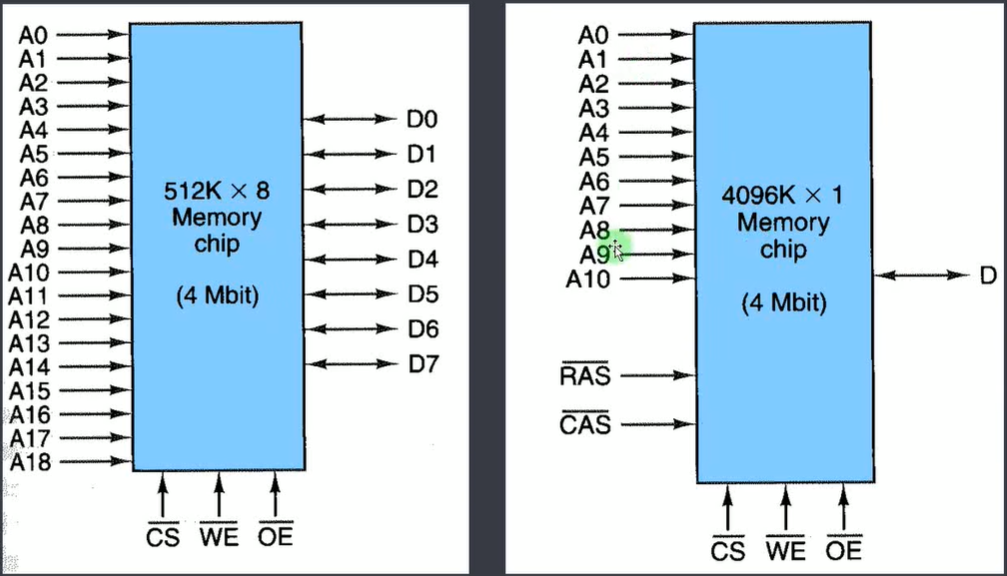

2. sram和ddr sdram结构图对比

主要是想对比sram和dram在和CPU连接过程的差异。sram需要的地址线较多,dram需要的较少,但是需要多次发送(行信号和列信号)。也因此dram需要内存控制器,而sram不需要。

3.内存泄漏

广义的内存泄漏:广义上的内存泄漏是指程序在申请内存后未能释放或无法释放,导致这部分内存不能被再次利用。内存泄漏是一个常见的软件问题,特别是在使用如C和C++这类需要手动管理内存的语言中更为常见。不过,内存泄漏也可以发生在其他语言中,比如Java、Python等,尽管这些语言通常有自动垃圾回收机制来管理内存。

狭义的内存泄漏:狭义的内存泄漏特指程序在运行过程中动态分配了内存,但在不再需要这些内存时没有正确地释放它们,导致这部分内存无法被操作系统回收再利用。这种现象主要出现在那些需要程序员手动管理内存的语言中,比如 C 和 C++。

解决之道

-裸机环境

-rtos平台

-linux/android平台