本文参考:

【图解CAN总线】-10-详解CANFD的TDC以及SSP(收发器延迟补偿和第二采样点)_canfd tdc-CSDN博客

“CAN 与 CAN FD 通信详解:协议、时间分析与延迟补偿机制“_canfd tdc-CSDN博客

1.TDC(Transceiver Delay Compensation)

1.1TDC的必要性:为何需要延迟补偿?

在CAN FD的数据段(Data Phase),比特率可高达8 Mbps,位时间(Bit Time)可能缩短至几十纳秒。此时,收发器环路延迟(Loop Delay) 成为瓶颈.这是因为在CAN总线通信中,有一种回读机制:指的是节点在向总线上发送报文的过程中,同时也对总线上的二进制位进行“回读”。 通过这种机制,节点就可以判断出本节点发出的二进制位与总线上当前的二进制位是否一致。如果收发器延迟时间过长,小于位时间,那就会读取错误。

例:

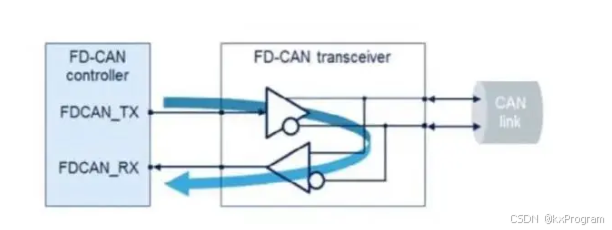

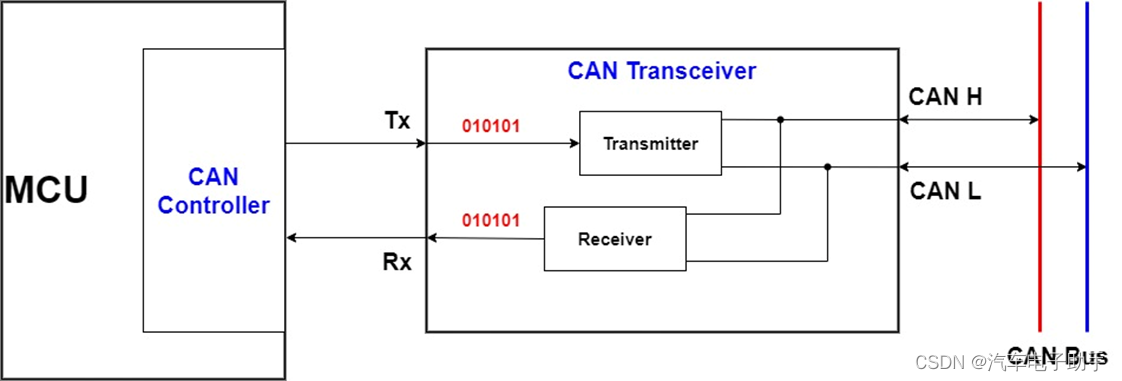

1.can控制器发送按照经典can/canfd帧格式,通过TX发送0和1数字电平序列给到CAN收发器

2.CAN收发器中的Transmitter将0和1数字电平序列转换差分电平,通过CANH和CANL发送到CAN Bus上

3.与此同时,CAN收发器中的Receiver回读CAN Bus上的差分电平,并转化为0和1数字电平,给到CAN控制器,完成一次“CAN报文的回采”;

4.CAN控制器比较Step1和Step3中TX和RX上数字电平是否一致

如果比较得数字电平不一致,就会出现错误

图1-1

1.2什么时收发器环路延迟(Loop Delay)

loop delay环路延迟的概念:

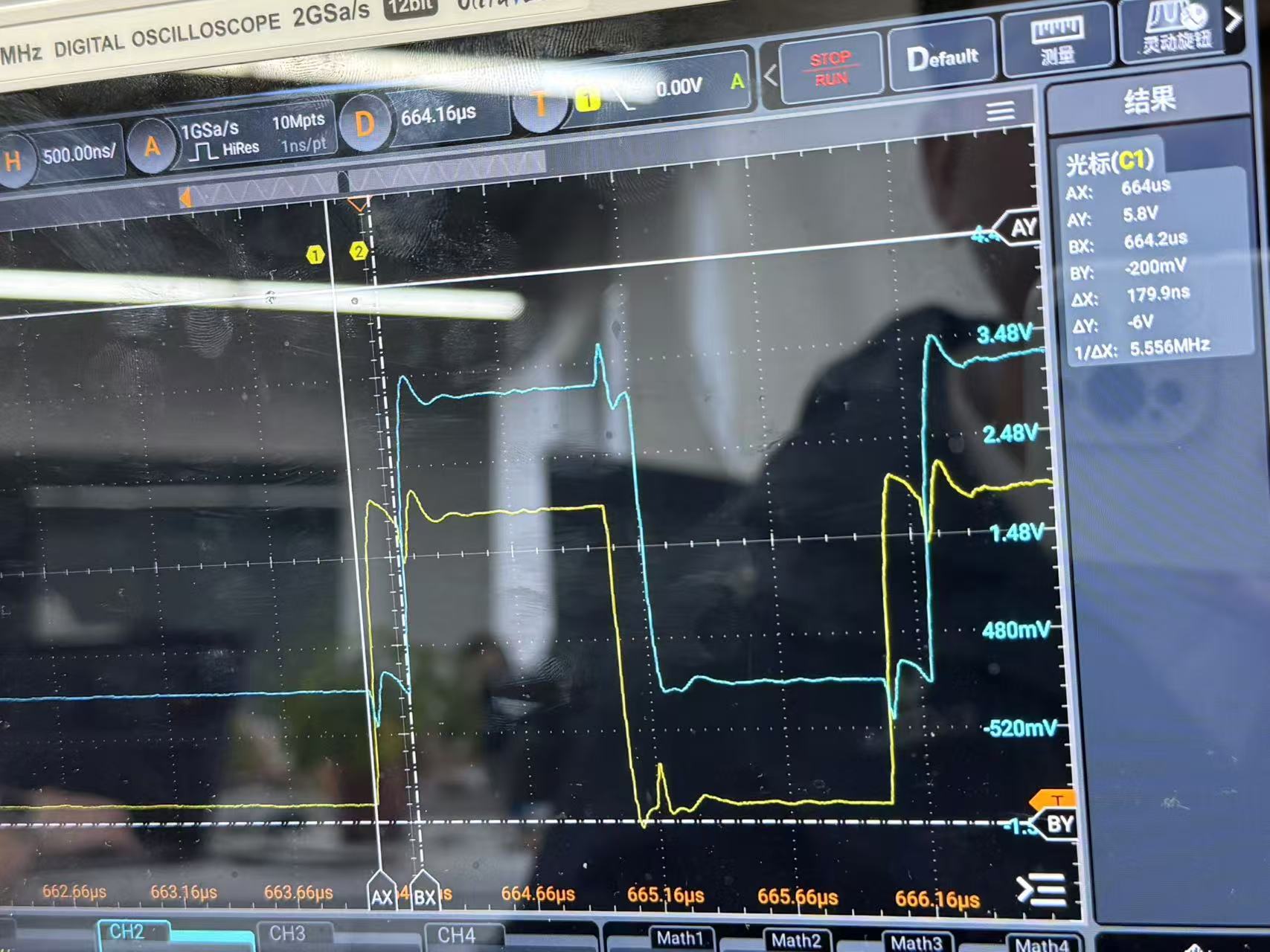

在“回采”过程中,CAN收发器经历了两次转换:Transmitter将0和1数字电平序列转换差分电平;Receiver将差分电平转换0和1数字电平序列。因为转换是需要时间的,势必有物理上的延迟。见图1-2,发送一帧报文。TX和Rx Pin上电平变化:Rx上的数字电平变化会滞后180ns。

图1-2

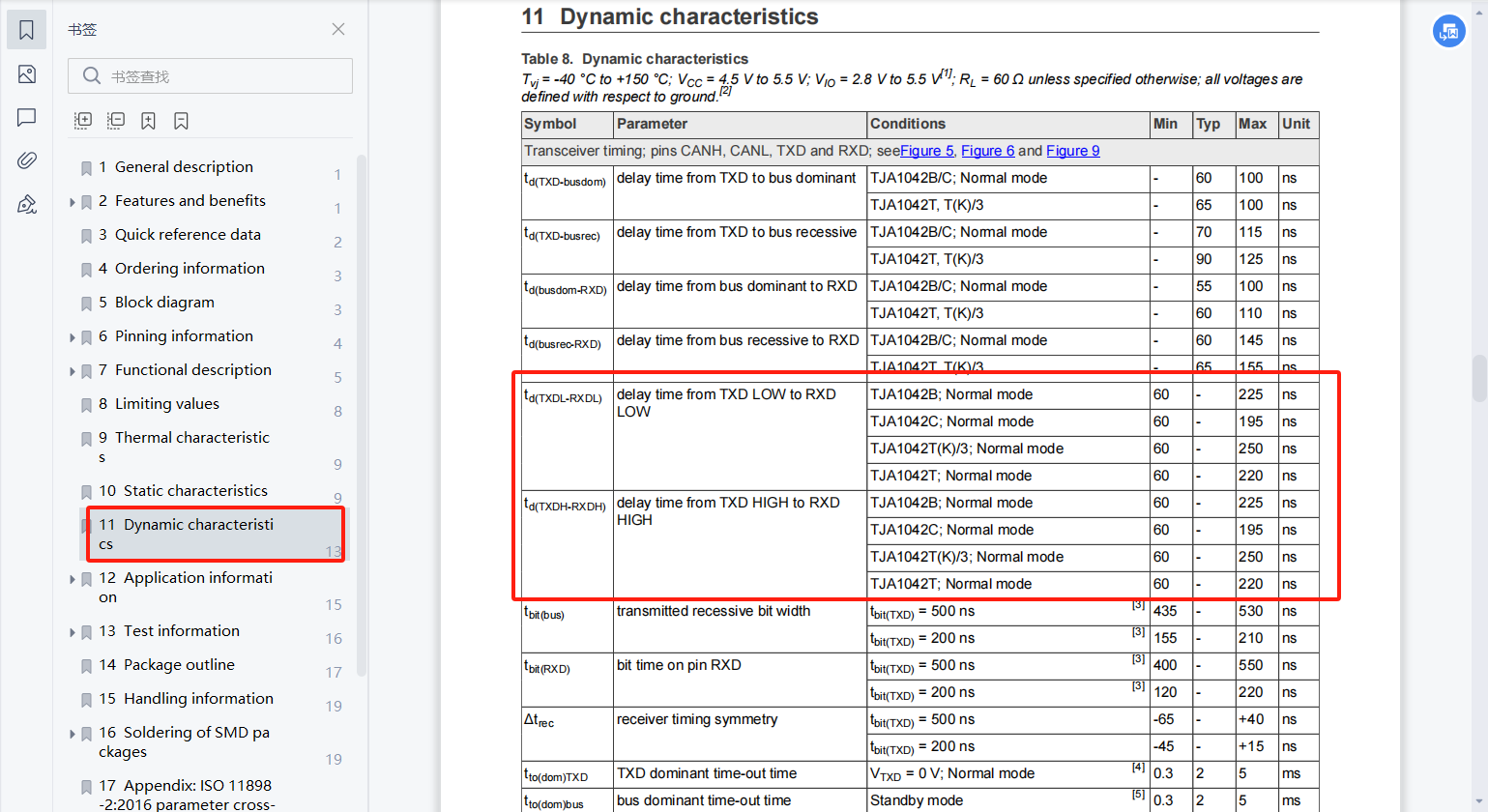

1.3环路延迟典型值

根据使用得收发器型号,查看手册,这里使用的是TJA1042

从这里可以看出收发器环路延迟最低60ns,最高225ns

1.4TDC的实现机制:如何补偿延迟?

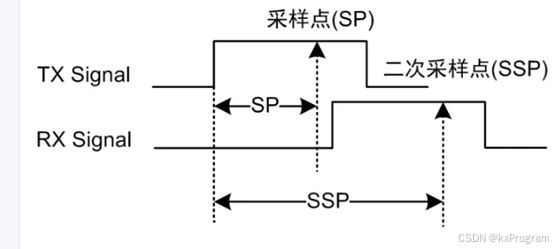

TDC通过引入第二采样点(Secondary Sample Point, SSP) 替代原始采样点,解决延迟问题。具体步骤如下:

1. 环路延迟测量

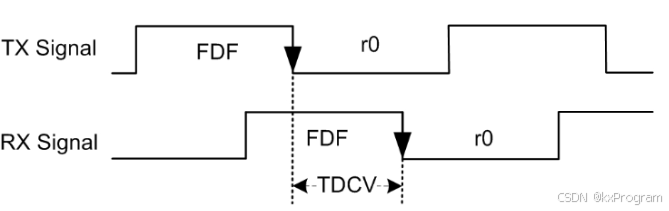

- 测量时机:在CAN FD帧的BRS位(Bit Rate Switch)下降沿至后续位(如r0位)的边沿之间,测量发送信号(TXD)与回采信号(RXD)的延迟时间(TDCV)

- 硬件支持:控制器内置计时器自动捕获延迟值,单位为时间量子(Time Quantum, Tq)

2. SSP计算与补偿

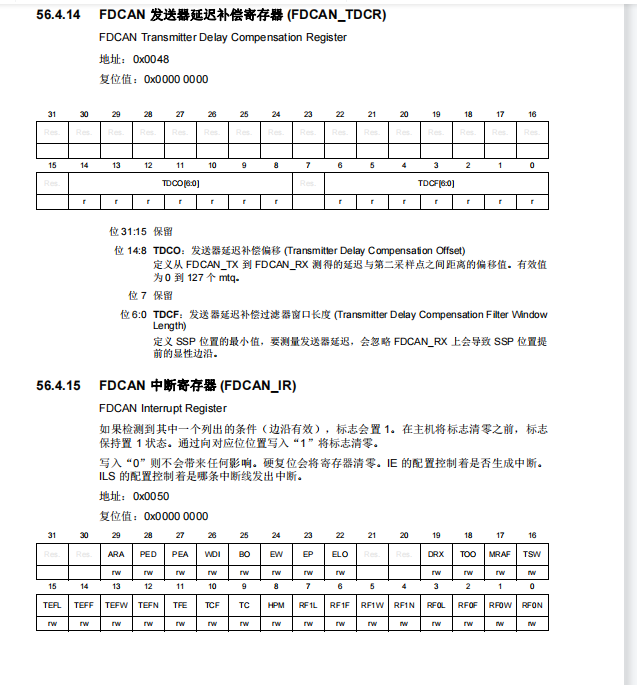

- 公式:SSP = TDCV + TDCO

- TDCV:实测环路延迟(转换为Tq单位)。

- TDCO(Transceiver Delay Compensation Offset):用户配置的偏移量,用于将SSP调整到位时间中间区域,避开边沿噪声

- 推荐配置:TDCO = Phase_Seg1 + Prop_Seg + 2(确保SSP位于位时间70%-90%区间)

实际计算:TDCO = 收发总延迟/tq

3. 错误检测优化

- 在数据段,控制器不再使用原始采样点,而是通过SSP比较发送位与回采位,避免因延迟导致的误判

2.Tq(Time Quantum)

2.1Tq的定义与作用

*时间量子(Tq)**是CAN FD控制器的最小时间单位,用于划分一个位周期的各个段(如同步段、传播段、相位缓冲段等)。每个段的时间长度由多个Tq构成,通过调整Tq的数量和频率,可以灵活配置总线波特率。

在CAN FD中,位时间分为两种模式:

- 仲裁段(Arbitration Phase):沿用传统CAN的低速波特率,用于总线竞争和帧头传输。

- 数据段(Data Phase):切换到更高波特率,支持更大数据载荷(最高64字节)和更快的传输速度(如5-8 Mbps)

2.2 Tq的计算方式

Tq的计算公式为: Tq=(BRP+1)/fclock 其中:

- BRP(Baud Rate Prescaler):预分频系数,用于将系统时钟分频为CAN控制器的工作时钟。

- fclock:CAN控制器的输入时钟频率(例如MCU的系统时钟或专用CAN模块时钟)

关键参数说明:

-

BRP的作用: BRP决定了每个Tq的时长。

例如,若系统时钟为80 MHz,BRP设为3,则: Tq=(3+1)/80 MHz=50 ns 这意味着每个Tq的时间为50 ns,位时间由多个Tq累加构成 -

仲裁段与数据段的差异:

- 仲裁段通常使用较大的BRP值以降低波特率(如500 kbps),确保总线竞争可靠。

- 数据段则采用较小的BRP值以提高波特率(如2 Mbps),并通过**Bit Rate Switch (BRS)**动态切换

-

分段配置示例: 假设仲裁段配置为500 kbps,数据段为2 Mbps:

- 仲裁段:BRP=4,Tq=100 ns,总位时间=20 Tq → 位时间=2 μs → 波特率=500 kbps。

- 数据段:BRP=1,Tq=25 ns,总位时间=10 Tq → 位时间=0.25 μs → 波特率=4 Mbps

2.3 Tq与位时序的关联

CAN FD的位时间由以下段组成,每个段以Tq为基本单位:

- 同步段(SYNC_SEG):固定1 Tq,用于节点间时钟同步。

- 传播段(PROP_SEG):补偿信号在总线上的物理延迟(如线缆传输和收发器延迟)。

- 相位缓冲段1(PHASE_SEG1)和相位缓冲段2(PHASE_SEG2):用于动态调整采样点,吸收时钟偏差

3.stm32配置和开启TDC功能

3.1使能函数

HAL_FDCAN_EnableTxDelayCompensation

/*** @brief Enable the transmitter delay compensation.* @param hfdcan pointer to an FDCAN_HandleTypeDef structure that contains* the configuration information for the specified FDCAN.* @retval HAL status*/

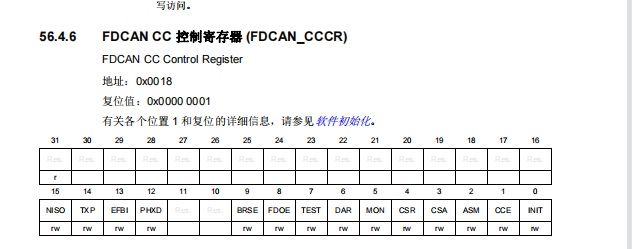

HAL_StatusTypeDef HAL_FDCAN_EnableTxDelayCompensation(FDCAN_HandleTypeDef *hfdcan)

{if (hfdcan->State == HAL_FDCAN_STATE_READY){/* Enable transmitter delay compensation */SET_BIT(hfdcan->Instance->DBTP, FDCAN_DBTP_TDC);/* Return function status */return HAL_OK;}else{/* Update error code */hfdcan->ErrorCode |= HAL_FDCAN_ERROR_NOT_READY;return HAL_ERROR;}

}3.2 TDC配置函数

HAL_FDCAN_ConfigTxDelayCompensation

/*** @brief Configure the transmitter delay compensation.* @param hfdcan pointer to an FDCAN_HandleTypeDef structure that contains* the configuration information for the specified FDCAN.* @param TdcOffset Transmitter Delay Compensation Offset.* This parameter must be a number between 0x00 and 0x7F.* @param TdcFilter Transmitter Delay Compensation Filter Window Length.* This parameter must be a number between 0x00 and 0x7F.* @retval HAL status*/

HAL_StatusTypeDef HAL_FDCAN_ConfigTxDelayCompensation(FDCAN_HandleTypeDef *hfdcan, uint32_t TdcOffset,uint32_t TdcFilter)

{/* Check function parameters */assert_param(IS_FDCAN_MAX_VALUE(TdcOffset, 0x7FU));assert_param(IS_FDCAN_MAX_VALUE(TdcFilter, 0x7FU));if (hfdcan->State == HAL_FDCAN_STATE_READY){/* Configure TDC offset and filter window */hfdcan->Instance->TDCR = ((TdcFilter << FDCAN_TDCR_TDCF_Pos) | (TdcOffset << FDCAN_TDCR_TDCO_Pos));/* Return function status */return HAL_OK;}else{/* Update error code */hfdcan->ErrorCode |= HAL_FDCAN_ERROR_NOT_READY;return HAL_ERROR;}

}4.自动重发

4.1 CAN总线重发机制的基本原理

CAN总线重发机制是一种基于硬件的数据传输方式,它可以确保在噪声干扰和其他不稳定因素影响下,数据的可靠传输。原理是:当CAN总线中发送一帧数据时,重发机制会在指定时间内重新发送这一帧数据,如果接收方收到了数据,则会发送一个确认帧,如果没有收到数据,则会继续重发,直到收到确认帧为止。因此,CAN总线重发机制可以有效提高数据的可靠性。

4.2 CAN总线重发机制的优点

1. 高效率

CAN总线重发机制可以有效提高数据传输的效率,因为它可以在指定时间内重新发送这一帧数据,从而提高数据的可靠性。

2. 可靠性

CAN总线重发机制可以在噪声干扰和其他不稳定因素影响下,保证数据的可靠传输。

4.3 触发报文自动重发的主要原因

1. 错误帧触发重发

(1)错误类型

- 位错误(Bit Error):发送节点在回读总线电平时发现与发送位不一致(如电磁干扰或收发器延迟导致),触发错误帧并重发

- 填充错误(Stuff Error):连续5个相同极性位后未插入填充位,接收节点检测到后发送错误帧

- CRC错误:接收节点计算的CRC校验值与发送节点不一致,触发重传

- 格式错误(Form Error):报文格式不符合标准(如界定符异常),导致接收节点拒绝确认

(2)错误帧的影响

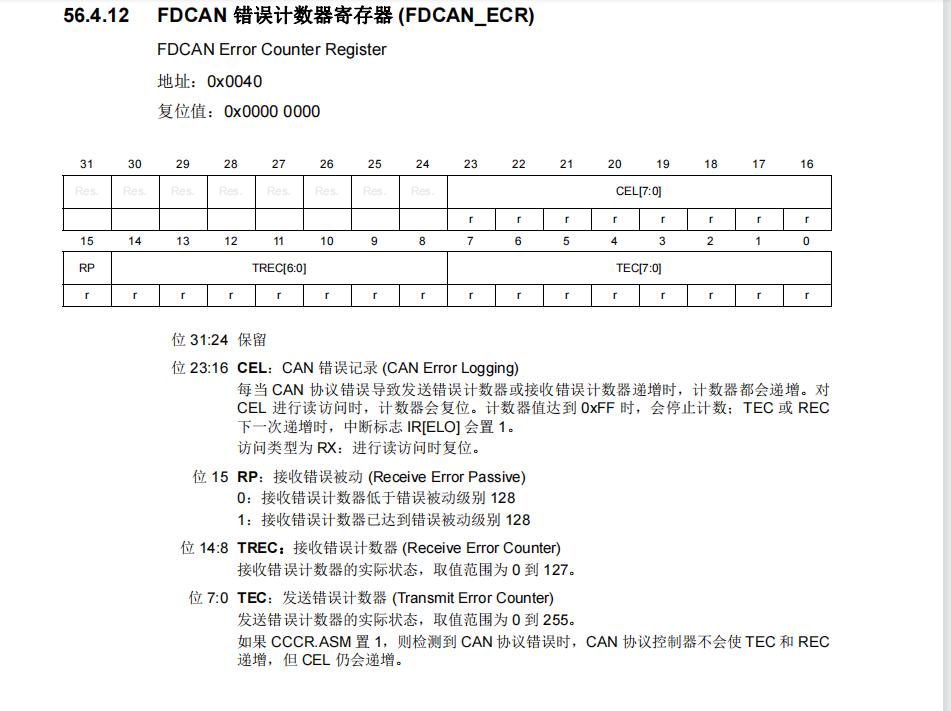

- 错误帧由接收节点主动发送,强制终止当前传输,发送节点根据错误计数器(TEC/REC)状态判断是否重发

2. ACK缺失

- ACK未响应:发送节点在ACK间隙(ACK Slot)未检测到显性位,认为报文未被正确接收,触发自动重发

- 原因:接收节点故障、总线断线或终端电阻不匹配(如缺少120Ω终端电阻导致信号反射)

- 极端情况:总线上仅有一个节点时,ACK无法被填充,导致持续重发

3. 总线负载过高

- 高负载导致仲裁失败:当总线负载率超过30%(经验阈值),低优先级报文可能因仲裁失败而延迟发送,若未及时收到ACK则重发

- 报文积压:频繁错误帧或重传会进一步增加负载,形成恶性循环

4. 物理层问题

- 线缆故障:断线、线缆过长(如CAN FD数据段超过40米)或非标准线缆(非双绞线)导致信号衰减或反射,引发错误帧

- 电磁干扰(EMI):强干扰源导致信号畸变,触发位错误或CRC错误

- 终端电阻异常:终端电阻不匹配(如两端未接120Ω电阻)导致信号反射,影响ACK响应

5. 配置错误

- 波特率或采样点不匹配:

- 仲裁段与数据段波特率配置错误(如仲裁段1Mbps,数据段未正确切换至5Mbps)导致时序不同步

- 采样点设置不当(如数据段采样点未达75%-90%范围),导致位采样错误.

- TDC未启用或参数错误:

- 未启用发送延迟补偿(TDC)或TDCO偏移量配置错误,导致高速数据段回读时序偏差,引发位错误

6. 总线关闭恢复后的重传

- Bus-off恢复:节点因连续错误进入总线关闭状态(TEC>255),恢复后需重传未确认的报文

- 错误计数器溢出:节点进入被动错误状态(TEC≥127),仍尝试重发但可能被高优先级报文覆盖

7. 协议兼容性问题

- 混合网络冲突:传统CAN节点无法解析CAN FD帧格式(如FDF位冲突),触发格式错误帧

- 相同ID冲突:多个节点使用相同ID发送报文,导致仲裁失败和错误帧

5.错误总结

5.1

1. 错误帧触发重发

(1)错误类型

- 位错误(Bit Error):发送节点在回读总线电平时发现与发送位不一致(如电磁干扰或收发器延迟导致),触发错误帧并重发

- 填充错误(Stuff Error):连续5个相同极性位后未插入填充位,接收节点检测到后发送错误帧

- CRC错误:接收节点计算的CRC校验值与发送节点不一致,触发重传

- 格式错误(Form Error):报文格式不符合标准(如界定符异常),导致接收节点拒绝确认

(2)错误帧的影响

- 错误帧由接收节点主动发送,强制终止当前传输,发送节点根据错误计数器(TEC/REC)状态判断是否重发

2. ACK缺失

- ACK未响应:发送节点在ACK间隙(ACK Slot)未检测到显性位,认为报文未被正确接收,触发自动重发

- 原因:接收节点故障、总线断线或终端电阻不匹配(如缺少120Ω终端电阻导致信号反射)

- 极端情况:总线上仅有一个节点时,ACK无法被填充,导致持续重发

3. 总线负载过高

- 高负载导致仲裁失败:当总线负载率超过30%(经验阈值),低优先级报文可能因仲裁失败而延迟发送,若未及时收到ACK则重发

- 报文积压:频繁错误帧或重传会进一步增加负载,形成恶性循环

4. 物理层问题

- 线缆故障:断线、线缆过长(如CAN FD数据段超过40米)或非标准线缆(非双绞线)导致信号衰减或反射,引发错误帧

- 电磁干扰(EMI):强干扰源导致信号畸变,触发位错误或CRC错误

- 终端电阻异常:终端电阻不匹配(如两端未接120Ω电阻)导致信号反射,影响ACK响应

5. 配置错误

- 波特率或采样点不匹配:

- 仲裁段与数据段波特率配置错误(如仲裁段1Mbps,数据段未正确切换至5Mbps)导致时序不同步

- 采样点设置不当(如数据段采样点未达75%-90%范围),导致位采样错误

- TDC未启用或参数错误:

- 未启用发送延迟补偿(TDC)或TDCO偏移量配置错误,导致高速数据段回读时序偏差,引发位错误

6. 总线关闭恢复后的重传

- Bus-off恢复:节点因连续错误进入总线关闭状态(TEC>255),恢复后需重传未确认的报文

- 错误计数器溢出:节点进入被动错误状态(TEC≥127),仍尝试重发但可能被高优先级报文覆盖

7. 协议兼容性问题

- 混合网络冲突:传统CAN节点无法解析CAN FD帧格式(如FDF位冲突),触发格式错误帧

- 相同ID冲突:多个节点使用相同ID发送报文,导致仲裁失败和错误帧

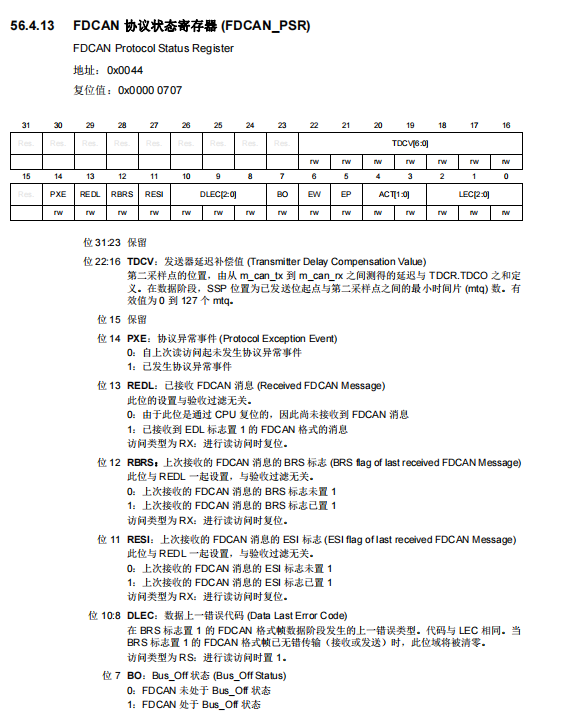

调试观察常用寄存器: