- 在Verilog硬件描述语言(HDL)中,信号的赋值方式主要分为两种:连续赋值和过程赋值。每种赋值方式有其独特的用途和语法,并适用于不同类型的电路描述。

1. 连续赋值(Continuous Assignment,assign 和=)

- 连续赋值主要用于描述

组合逻辑,通常与assign关键字一起使用。它在顶层模块或过程块外部进行,用于对wire类型的信号赋值。

特点:

- 组合逻辑:连续赋值用于实现组合逻辑,表示输出信号始终等于表达式的值。

- 实时更新:当右边的表达式中的任何信号发生变化时,左边的信号会立即更新。

- 信号类型:通常用于

wire类型信号。

示例

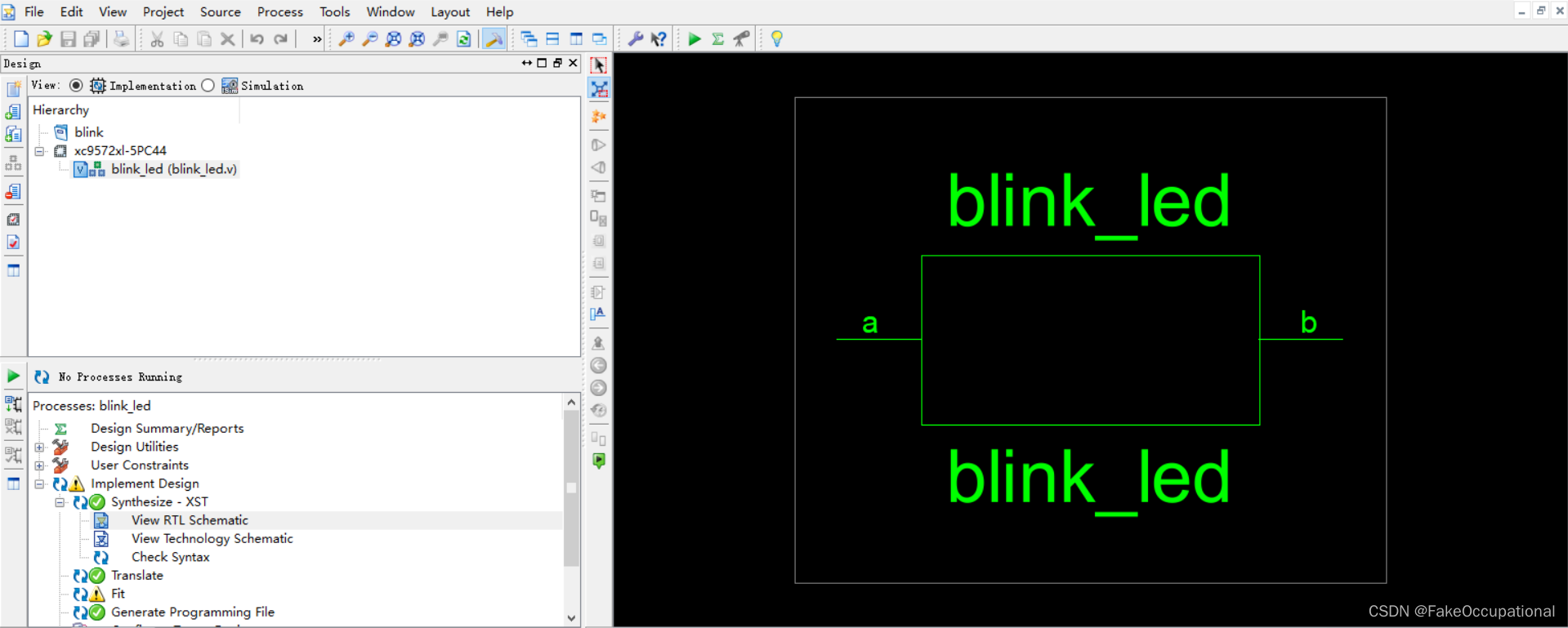

示例 1:

module blink_led(input wire a,output wire b

);assign b = a;endmodule

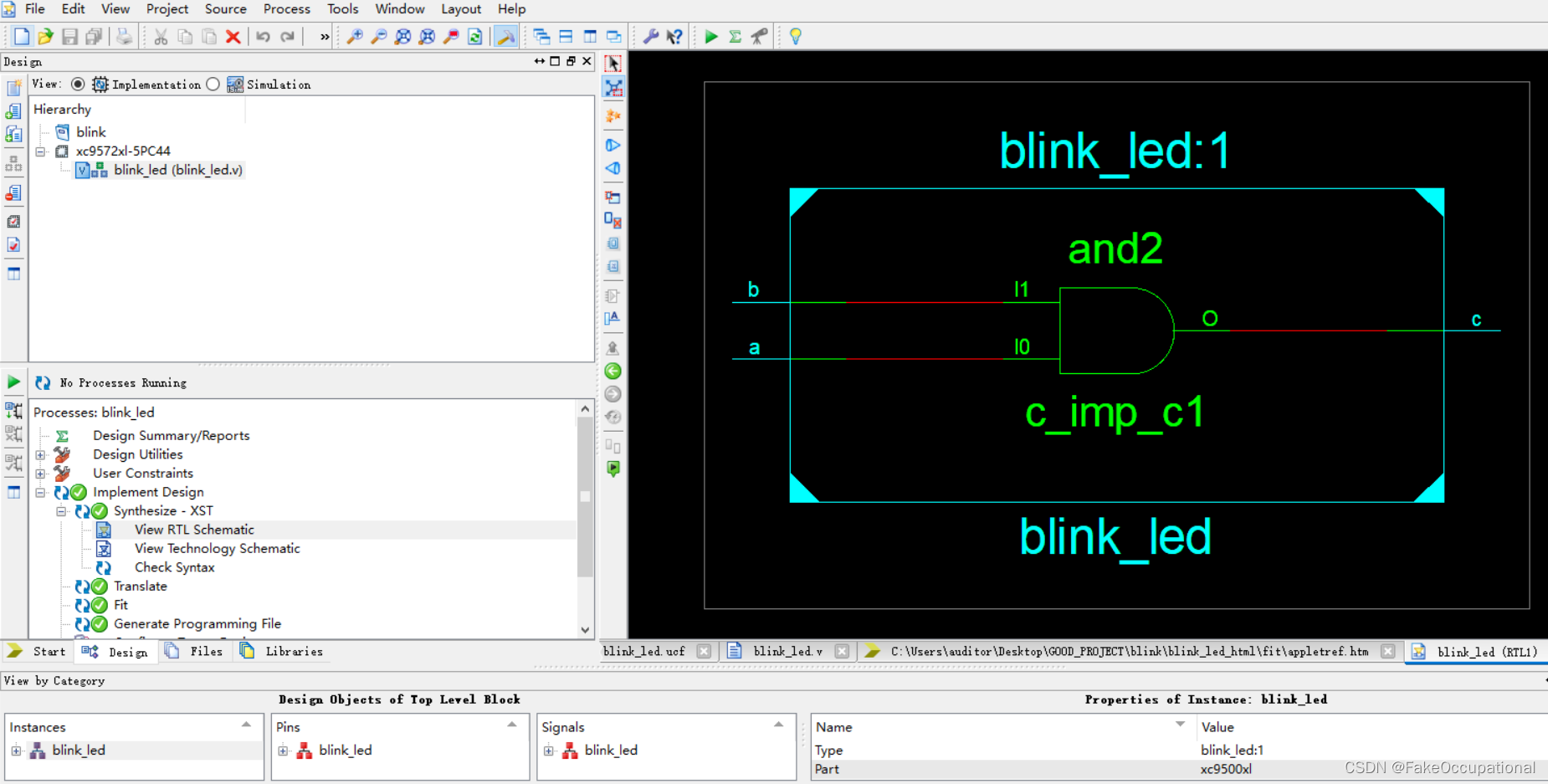

示例 2:

module combinational_logic (input wire a,input wire b,output wire c

);// c 始终等于 a 和 b 的逻辑与assign c = a & b;

endmodule

2. 过程赋值(Procedural Assignment)

- 过程赋值用于过程块(如

always或initial块)内,适用于描述组合逻辑或时序逻辑。过程赋值可以进一步分为两种:阻塞赋值(=)和非阻塞赋值(<=)。

2.1 阻塞赋值(Blocking Assignment,=)

特点 :

- 顺序执行:阻塞赋值按书写顺序执行,一个语句必须在前一个语句完成后才能执行下一个语句。

- 阻塞行为:在赋值完成之前,后续的语句不会执行。相当于“阻塞”了后续操作。

- 主要用于组合逻辑:通常用于描述组合逻辑,在

always @(*)块中使用。

示例 :

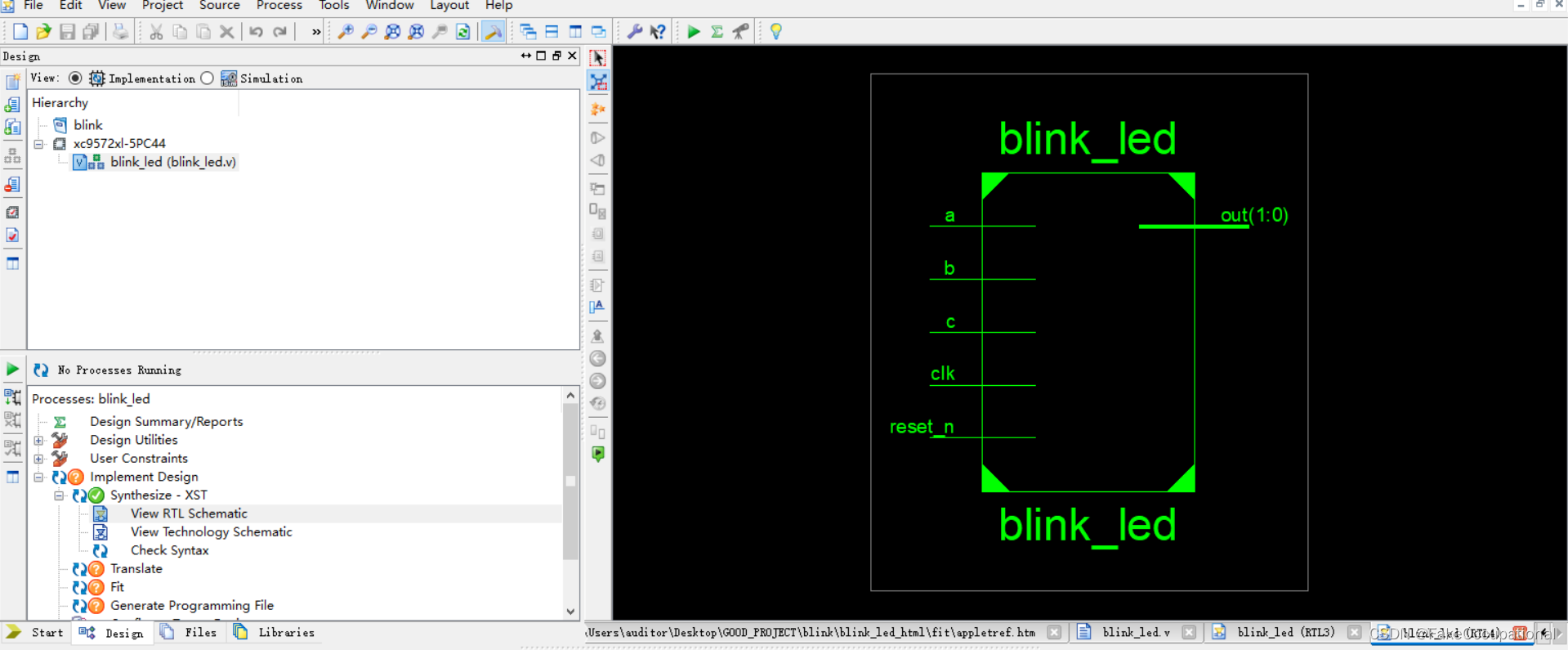

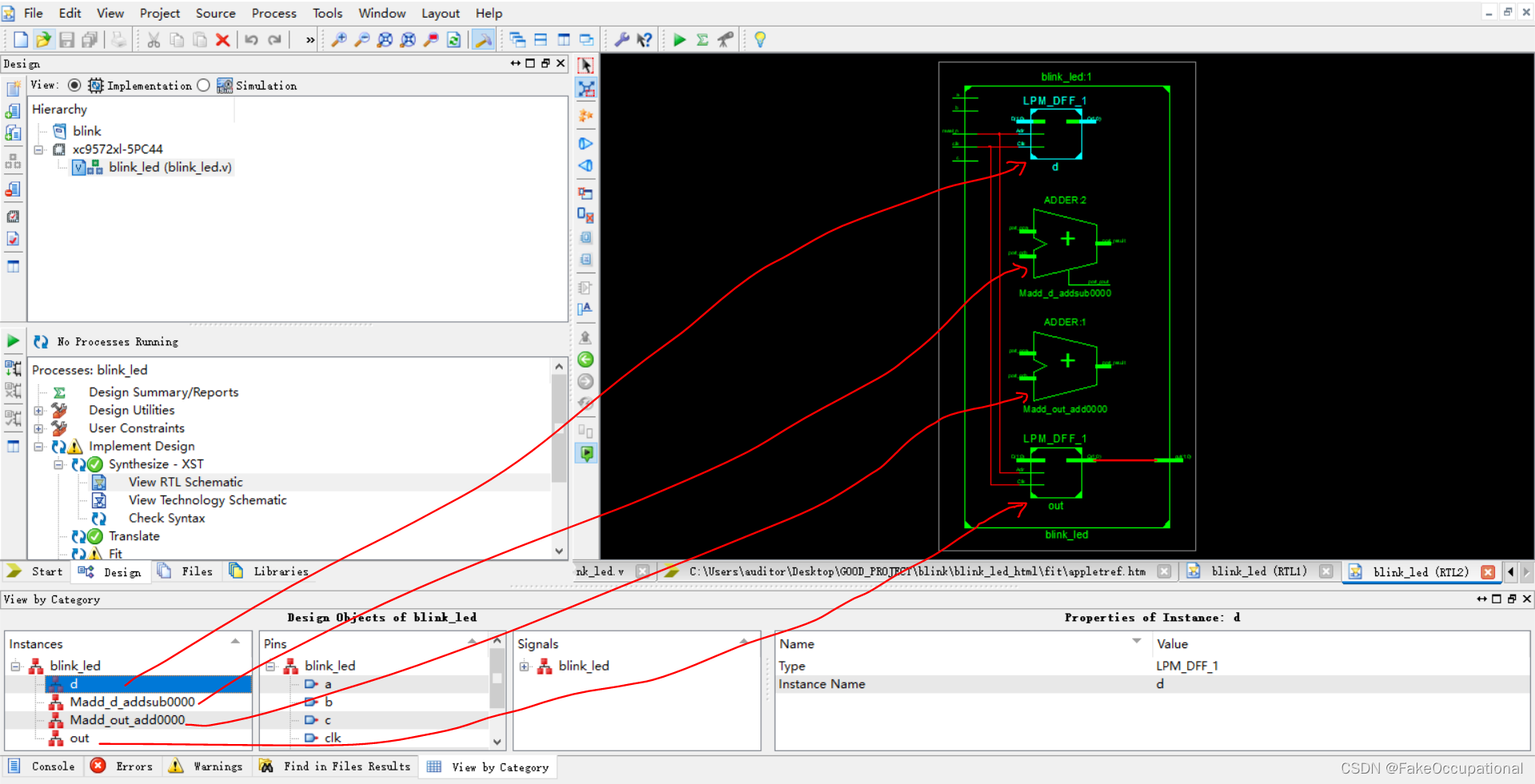

- 这个代码,阻塞赋值与下边的非阻塞赋值电路一样

module blink_led(

clk,reset_n,a,b,c,out);input clk;input reset_n;input a,b,c;output reg [1:0] out;reg [1:0] d;always@(posedge clk or negedge reset_n)if(!reset_n)beginout =2'b0;d =0; endelse beginout =d+c;d =a+b;endendmodule

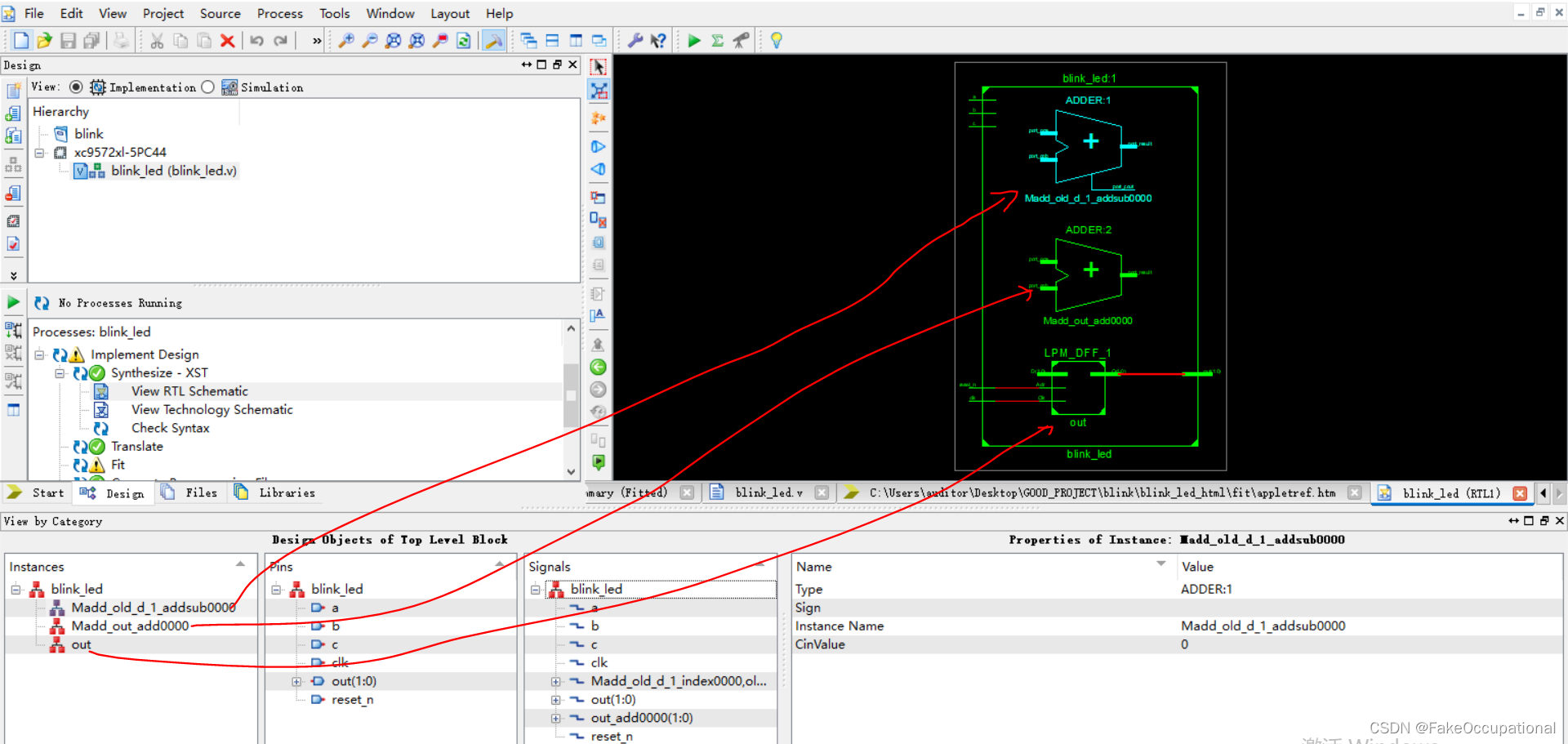

ISE的RTL Schematic

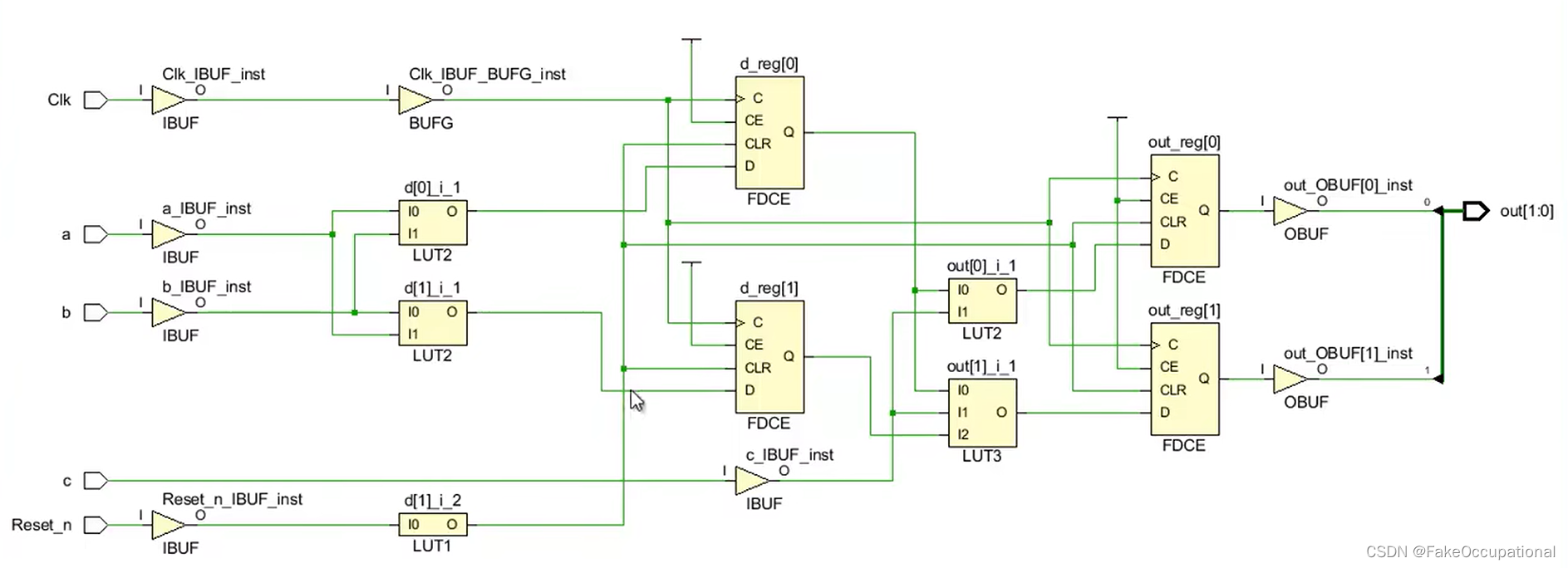

vivado的 Schematic

更换两句的顺序

module blink_led(

clk,reset_n,a,b,c,out);input clk;input reset_n;input a,b,c;output reg [1:0] out;reg [1:0] d;always@(posedge clk or negedge reset_n)if(!reset_n)beginout =2'b0;d =0; endelse begind =a+b;out =d+c; // 这里的 out 使用更新后的 d 值,电路图中少一一个寄存器endendmodule

ISE的RTL Schematic

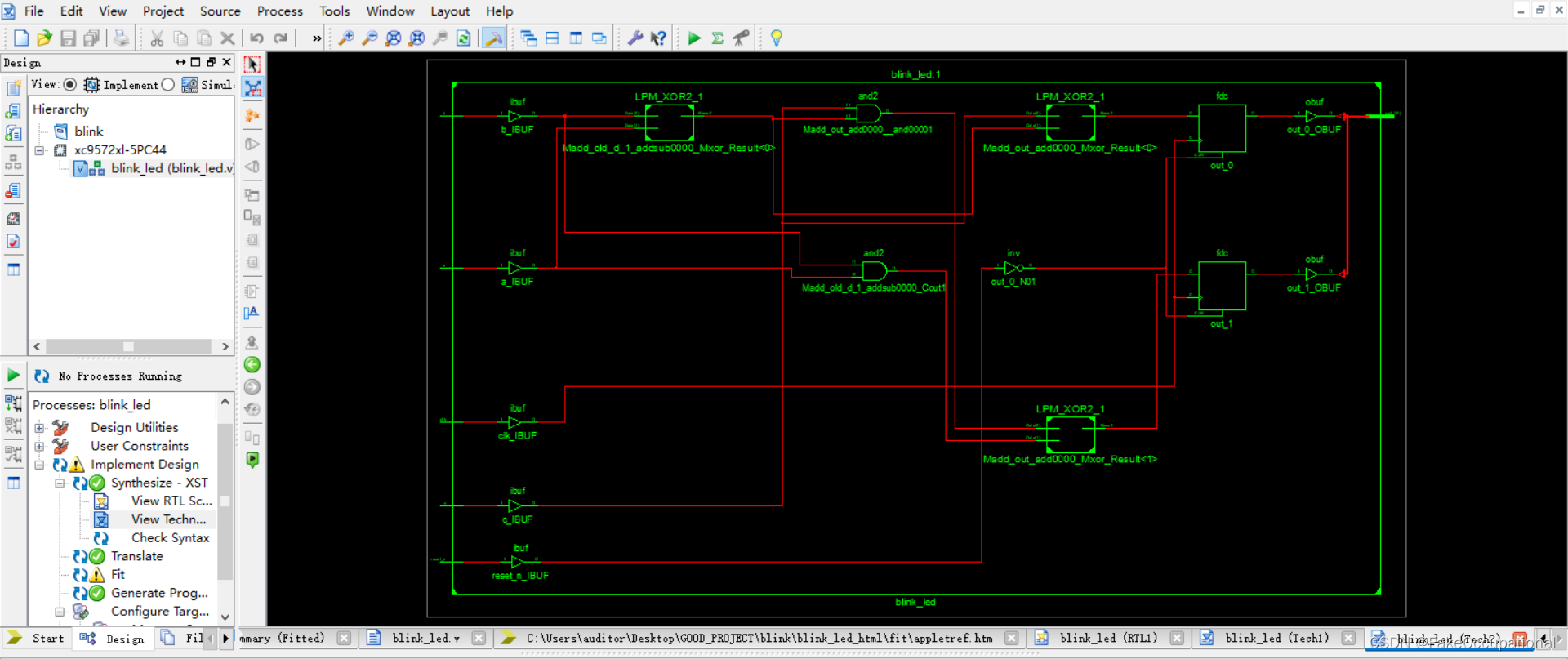

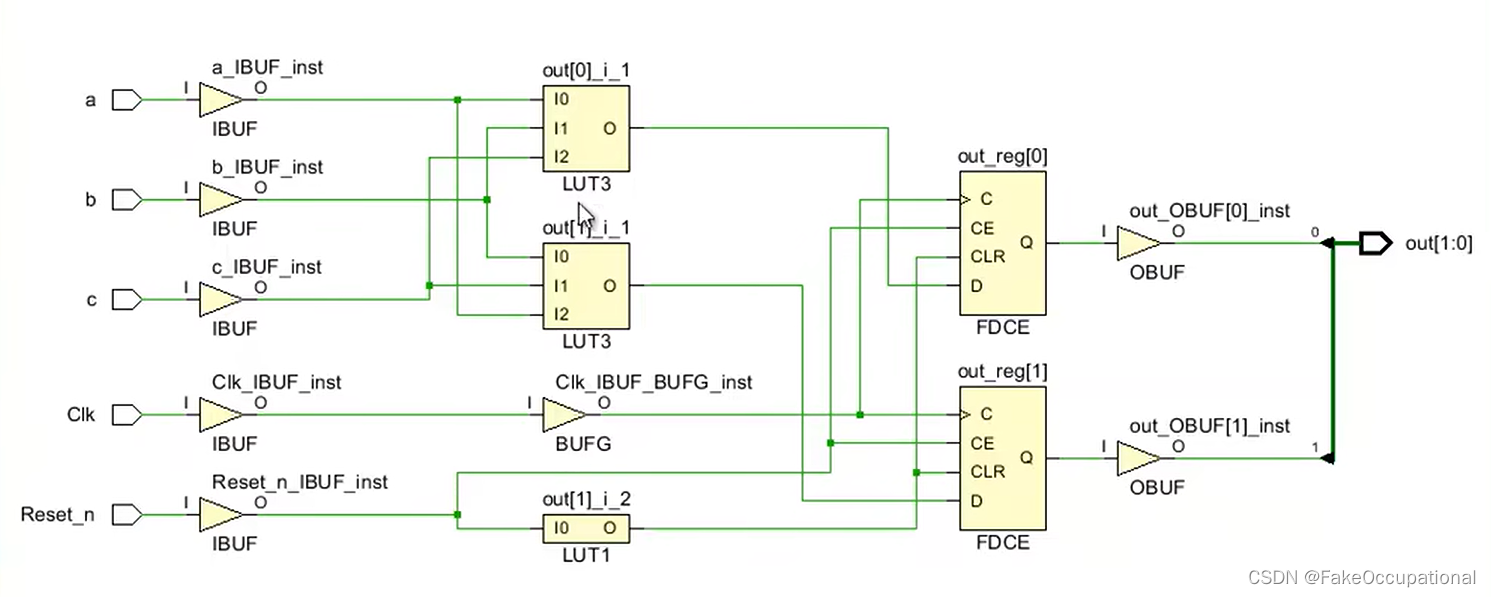

ISE的Technology Schematic

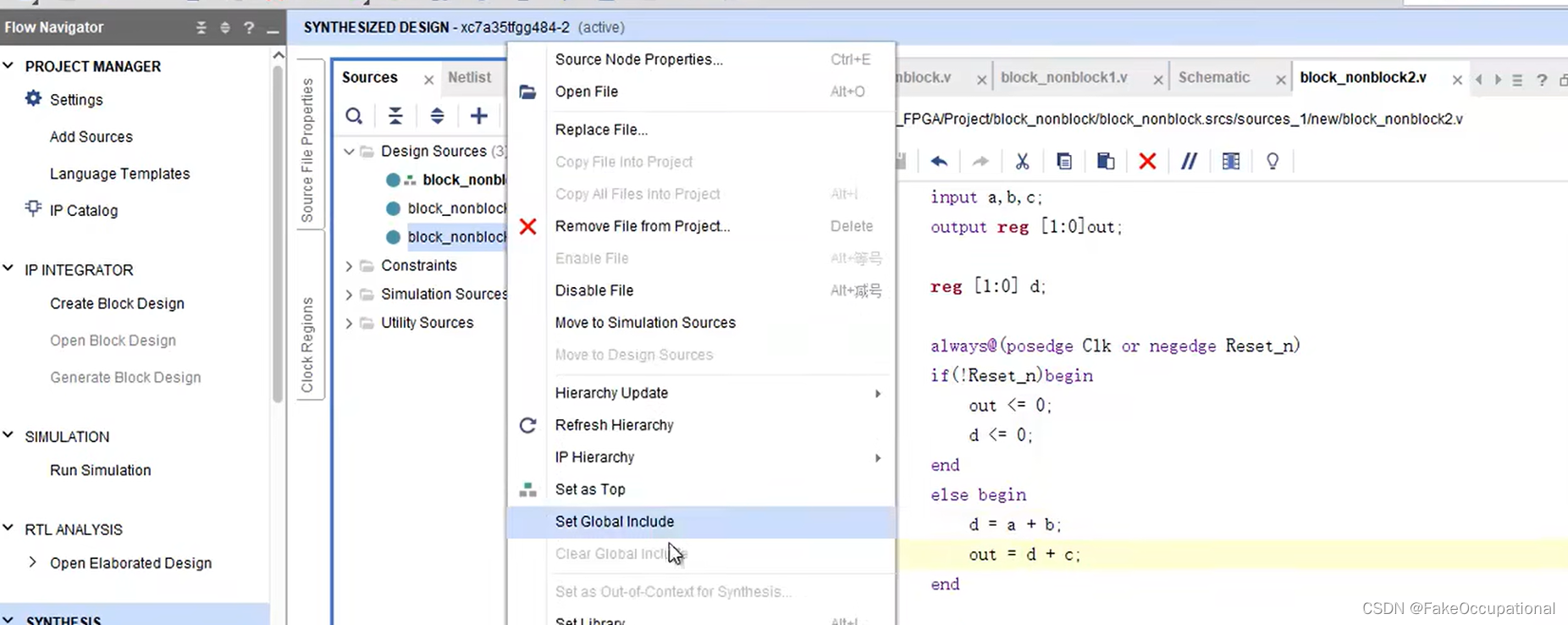

vivado

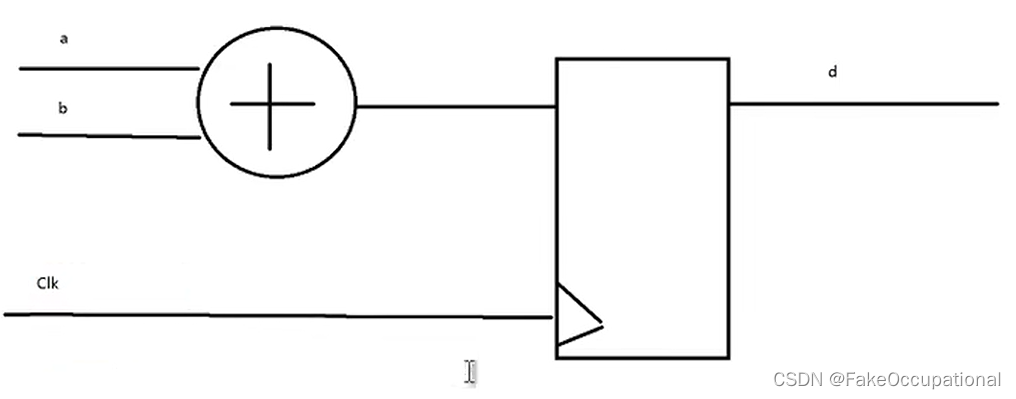

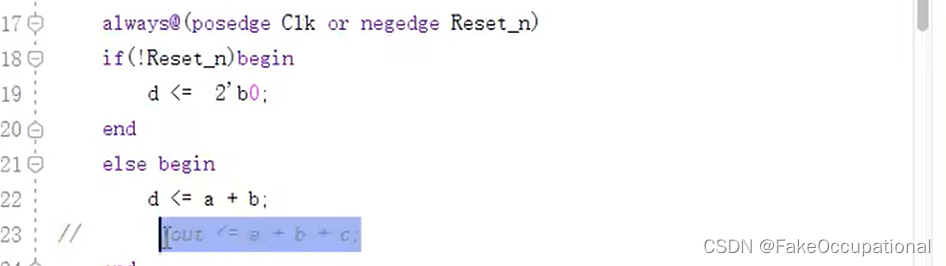

2.2 非阻塞赋值(Non-blocking Assignment,<=)

特点 :

- 并行执行:非阻塞赋值允许赋值操作并行执行,不必等待前一个语句完成。

- 主要用于时序逻辑:通常用于描述时序逻辑,在

always @(posedge clk)块中使用。

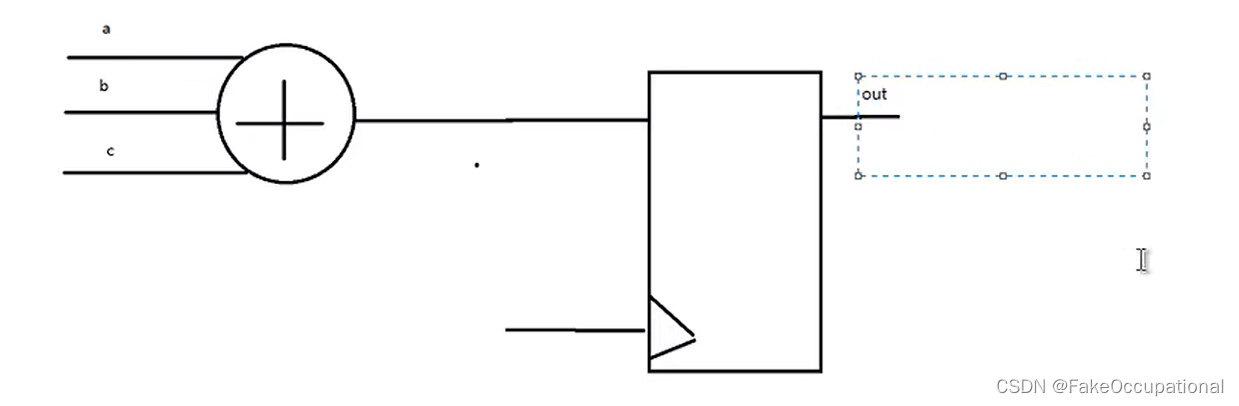

示例:

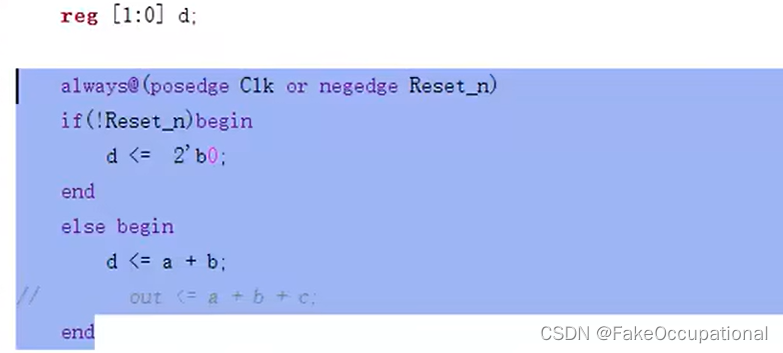

module mux2(

clk,reset_n,a,b,c,out);input clk;input reset_n;input a,b,c;output reg [1:0] out;reg [1:0] d;always@(posedge clk or negedge reset_n)if(!reset_n)beginout =2'b0;d =0; endelse begind <=a+b;out <=d+c;// 这里的 out 使用更新前的 d 值endendmodule

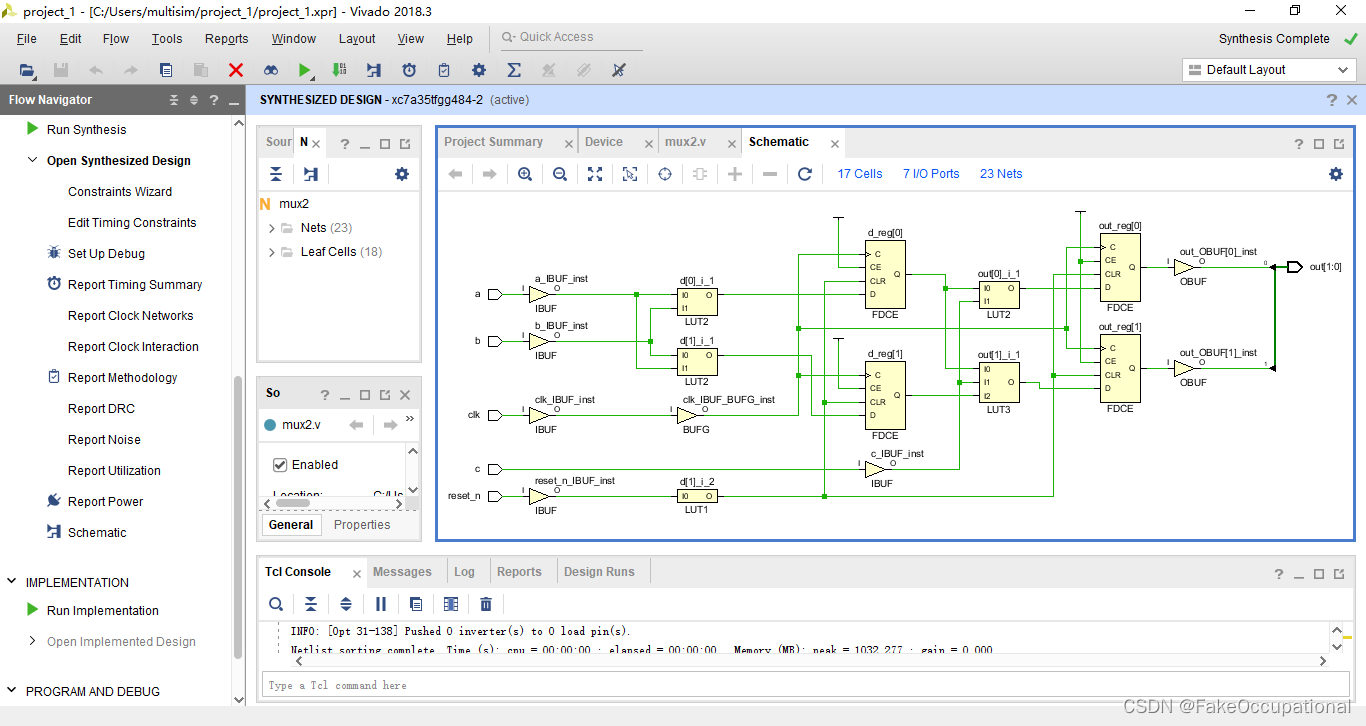

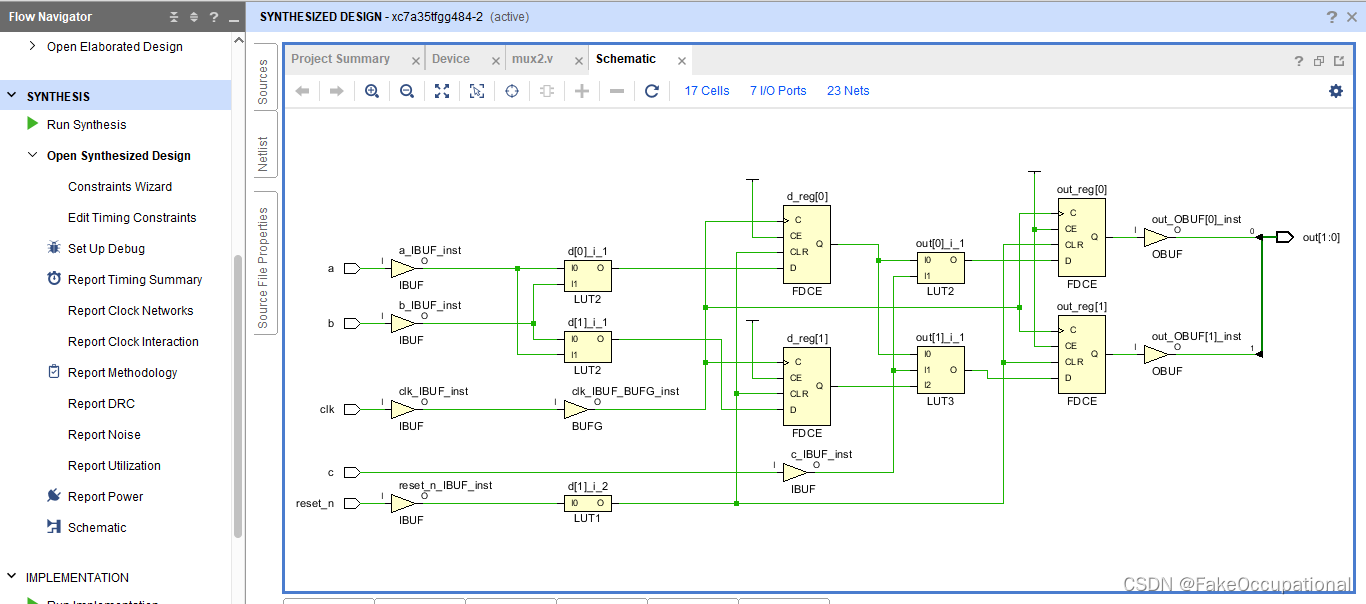

vivado

更换两句的顺序电路图没有改变

手绘示例

3.对比与应用场景

-

连续赋值 vs. 过程赋值:

- 连续赋值:用于

wire类型信号,描述组合逻辑。 - 过程赋值:用于

reg或integer等类型信号,描述组合或时序逻辑。

- 连续赋值:用于

-

阻塞赋值 vs. 非阻塞赋值:

- 阻塞赋值:用于组合逻辑,按顺序执行,通常在

always @(*)块中。 - 非阻塞赋值:用于时序逻辑,并行执行,通常在

always @(posedge clk)块中。

- 阻塞赋值:用于组合逻辑,按顺序执行,通常在

CG

- https://www.bilibili.com/video/BV1va411c7Dz?p=11