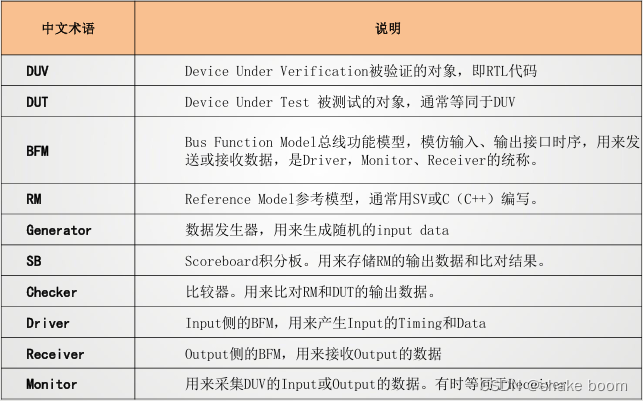

术语——中文术语

大陆与台湾的一些术语存在差别:

验证常用的英语术语:

验证:尽量模拟实际应用场景,比对芯片的所需要的目标功能和实现的功能

影响验证的要素:应用场景、目标功能、比对应用场景、目标功能:来源于产品需求、系统方案、设计实现;准确、完备、清晰、异常。

比对:设计与验证的隔离、独立性;比对效率

验证与测试:关注点的区别

验证类型:EDA验证、FPGA验证、芯片验证、软硬件结合验证

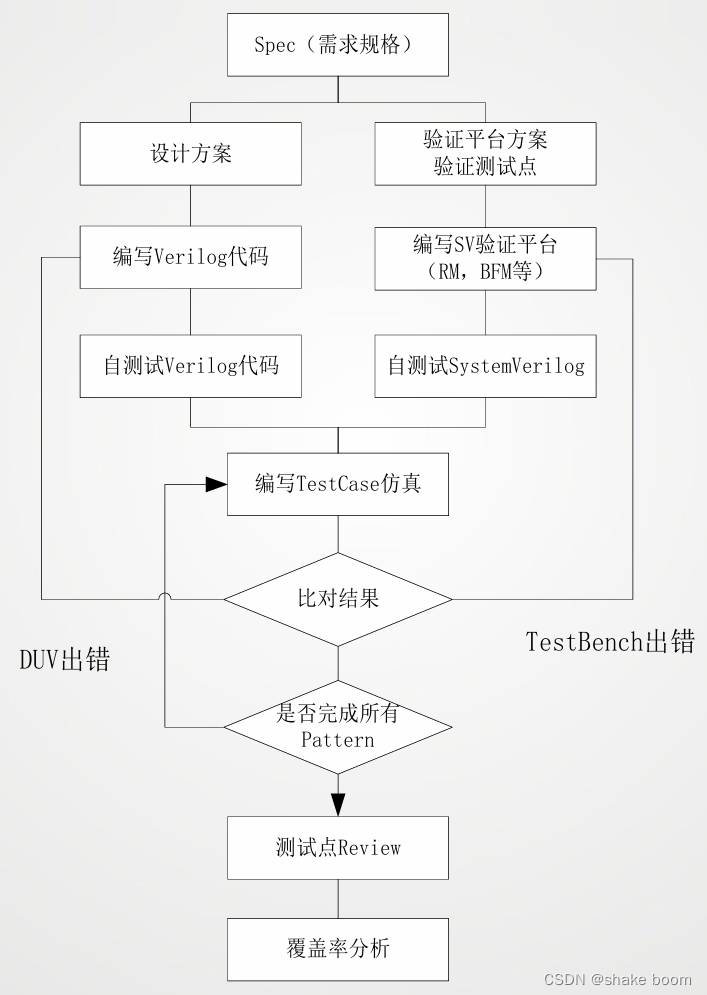

验证流程

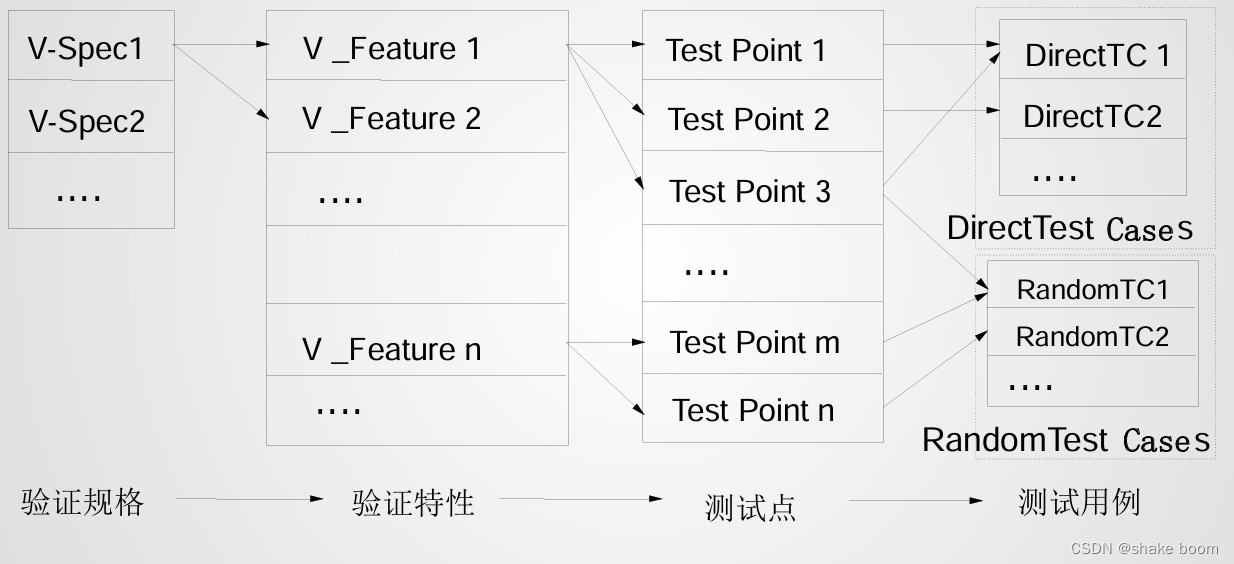

测试点:

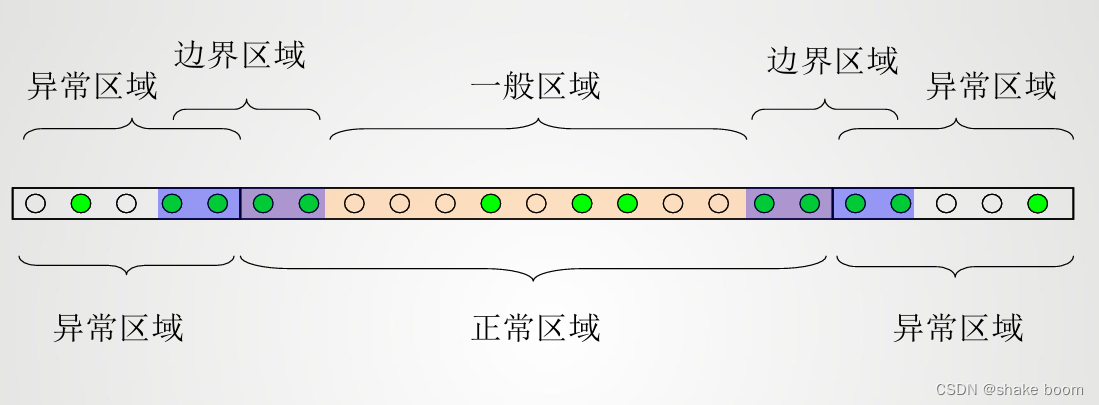

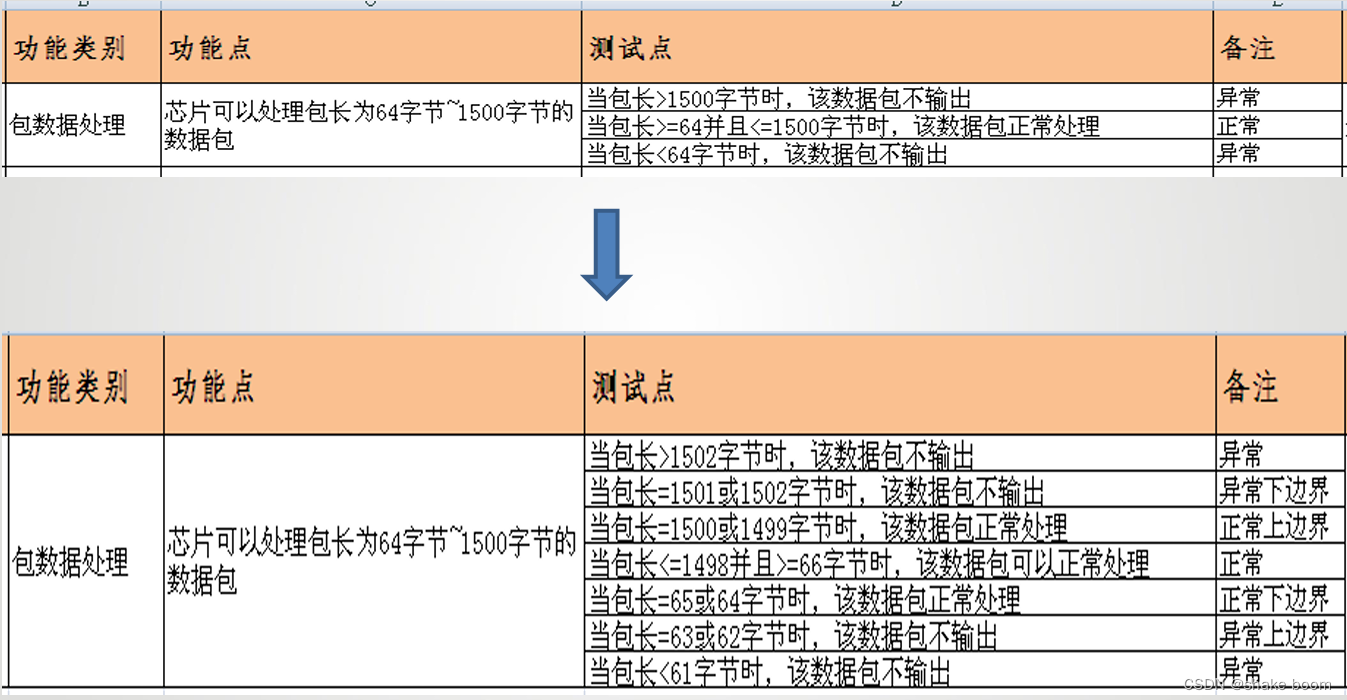

例如:芯片可以处理包长为64Bytes~1500Bytes的数据包,则验证时则可以划分成哪几个测试区间呢?(假设包长为16Bit位宽)。

测试点——分解测试点的方法

1,SPEC

文档上所有明确写出的SPEC

2,输入、配置、输出

所有合理的输入

所有合理的配置

所有合理的输出

所有合理的输入、配置的不同组合

3,场景

多个功能在同一时间段内的不同组合

多个功能在前后顺序之间的不同组合

4,异常

验证用例——定向验证

验证用例——随机验证

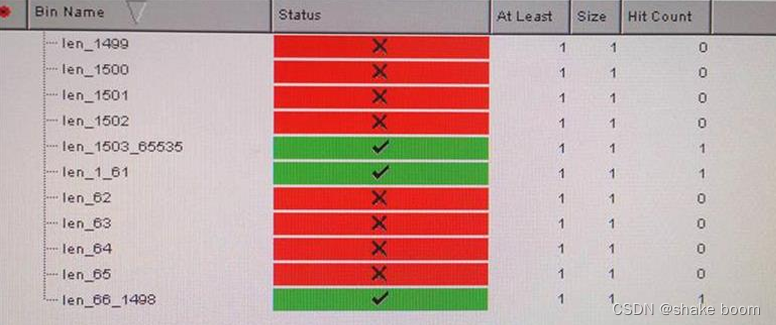

rand bit [15:0] pkt_len;

constraint c_pkt_len {pkt_len dist {[1:61] :/ 10,[62:63] :/ 10,[64:,65] :/ 10,[66:1498] :/ 10,[1499:1500] :/ 10,[1501:1502] :/ 10,[1502:65535] :/ 10,};

}

利用System Verilog的比例约束,可以灵活地设置每个区间的概率。

通过上述方法,发送同样的包个数,就能覆盖到所有的测试点。

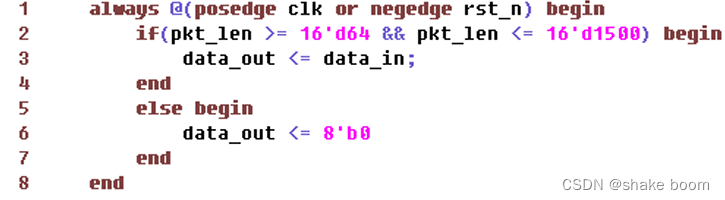

覆盖率——Code Coverage

发送三个数据包,包长分别为10、100、2000字节,就可以达到100%的

Code Coverage(如:Line Coverage、Conditon Coverage)

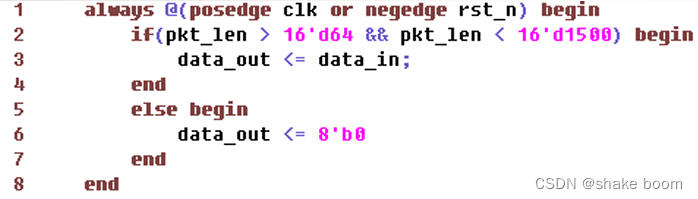

如果RTL不小心写成上面这样,而没有验证到,我们能发现吗?

覆盖率——Function Coverage

通过定义功能覆盖率,就可以发现上述的问题。

从需求,到测试点,到用例:总->分->总

测试点要求细而不漏。

测试点的交叉。例如不同类型包文有不同的长度范围和处理。变量越多组合

越多,测试向量就越多。

测试用例:随机为主定向为辅,还是随机为主定向为辅

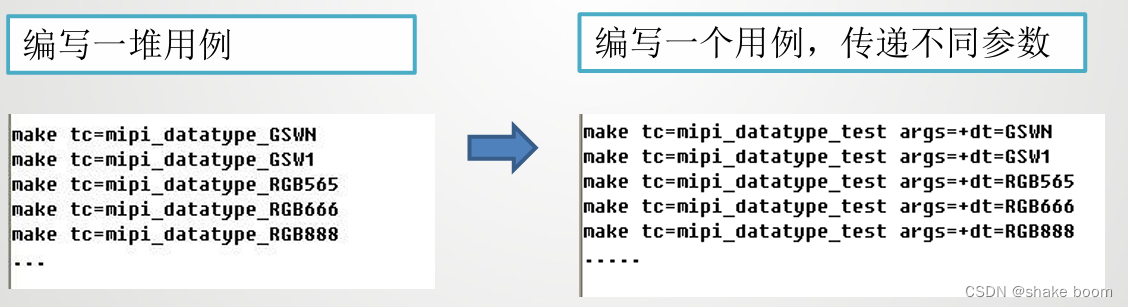

验证用例——脚本化

传统的用例设计方法:

根据测试点编写大量的TestCase来覆盖所列的测试点

用例脚本化:

设计一个通用用例模版,通过脚本,传递不同的参数配置。

一个TestCase生出大量TestCase,减少大量用例的编写、维护工作。

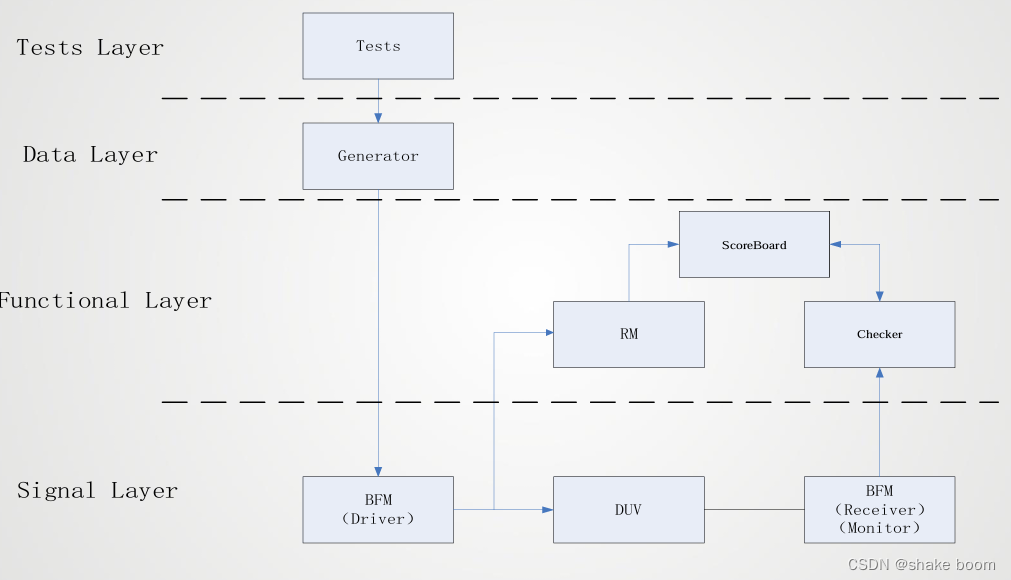

验证平台——架构

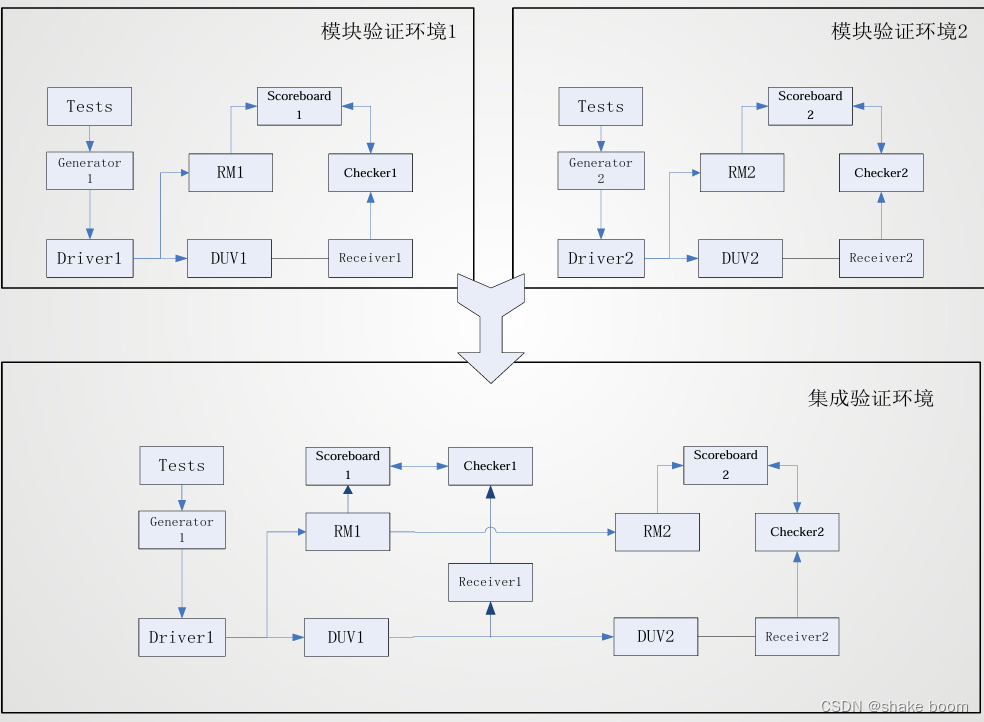

验证平台——集成

验证的模块化、完整性思维

模块化与完整性

结构上的模块化

数据类型上的模块化:配置、数据

流程上的模块化:

验证自动化——工具

1,Makefile

(1)支持批量仿真;

(2)每个TC单独生成一个LOG,一个波形,一组对应图像信息

(3)自动检查所有TC的LOG,生成所有TC的Pass or Fail的记录

(4)自动本地化

(5)在当前目录下,编辑打开其他目录的文件

…

2,Excell提取脚本

(1)寄存器信息列表

(2)数模接口连线复位值

(3)数模混仿Vector信息

3,自动连线脚本

(1) 连接各个module的verilog

4,其他Tcl、Perl脚本

验证自动化

1,Regression自动化

2,寄存器测试自动化

3,Log检查自动化

4,数据比对自动化

5,时序比对自动化

6,Co-SIM的Vector自动化

7,数字模拟接口连线检查自动化

服务自己的人机交互:

表格与仿真环境之间自动化

EXCEL+VBA

XML PARSER

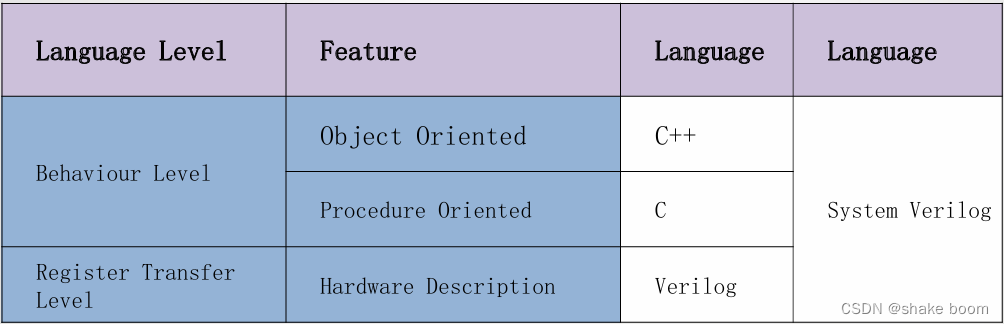

验证语言——System Verilog

HDVL:Hardware Description And Verification Language

完全兼容Verilog语言

支持Behaviour Level建模

支持面向对象编程,容易扩展、移植

支持各种随机方式:权重比例等

支持功能覆盖率

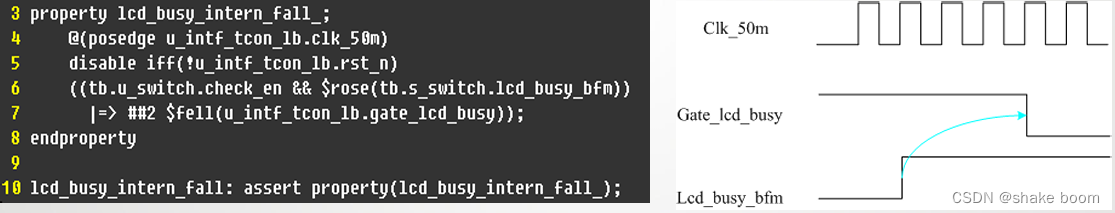

验证语言——SVA

System Verilog Assertions:简称SVA

用途:用来检查Timing的正确性。(区别:Reference Model用来检查Data的正确性)。如果Timing不正确会输出Fail信息。

SVA代码示例:

以上代码是检测check_en有效的时候, 每次lcd_busy_bfm 的上升沿之后

两个clk,必须有gate_lcd_busy 的上升沿。

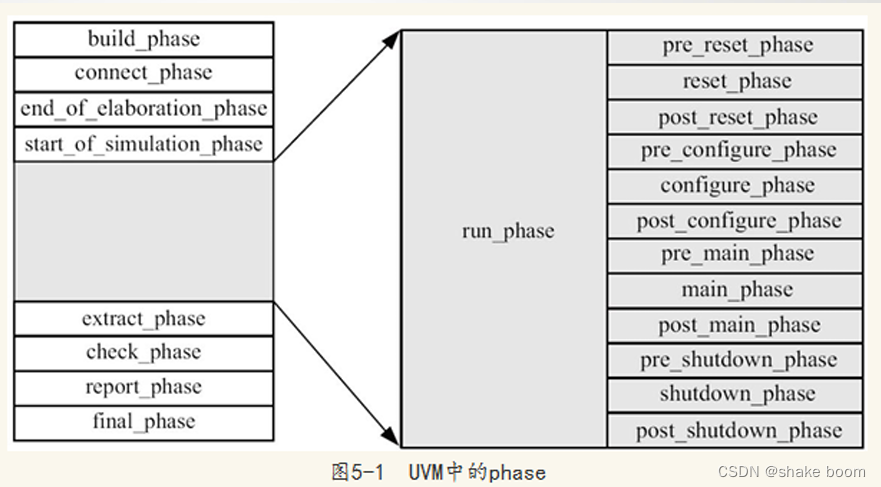

UVM

UVM:Universal Verification Methodology

来源:兼容VMM和OVM的优点

内容:验证方法学+验证平台模版+验证代码库

举例:盖房子

很早很早以前没有建筑学,大家的房子也是千奇百怪,各不相同,有在树上,有在地下,也有在树上。后来,慢慢开始有人归纳这些房子的特点,发现:大部分都有“门”、“窗户”,“房间”,“屋顶”等。所以,慢慢开始把房子分成这几个部分来研究,逐渐就形成一套房子的方法学。后来再总结各个部分优秀的建造方法,提供给大家做参考,或者直接做好各个部分,给大家用,就形成组件、模版。