零、计算机的发展

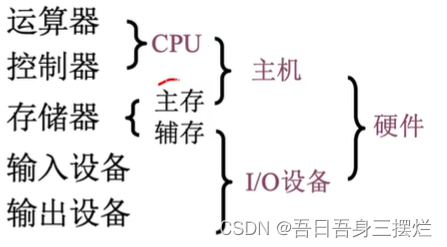

冯.诺依曼计算机的特点:

1.计算机由五大部件组成

2.指令和数据以同等地位存于存储器,可按地址寻访

3.指令和数据用二进制表示

4.指令由操作码和地址码组成

5.存储程序(首次提出存储结构)

6.以运算器为中心(现代计算机一般以存储器为核心,cpu=运算器+控制器)

7.

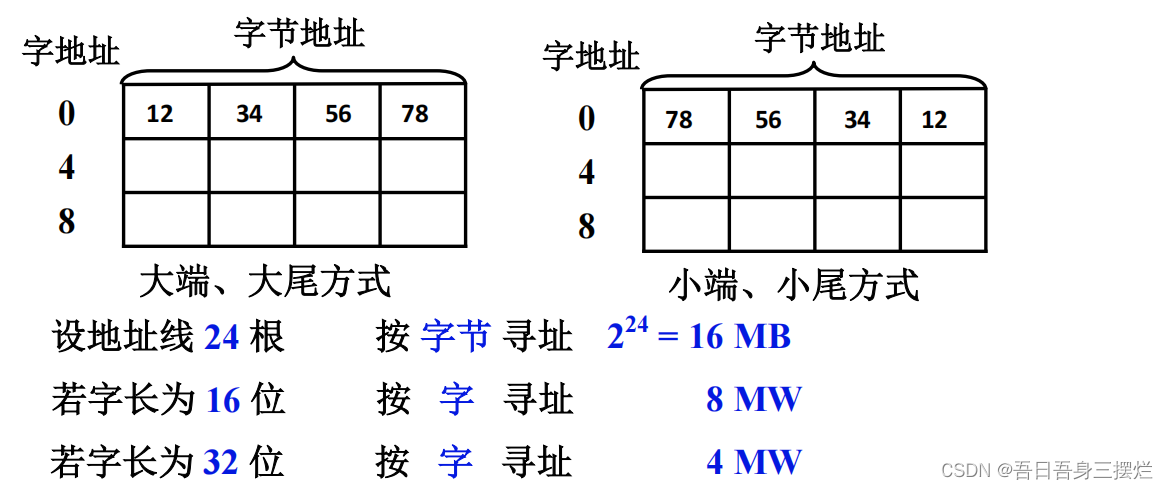

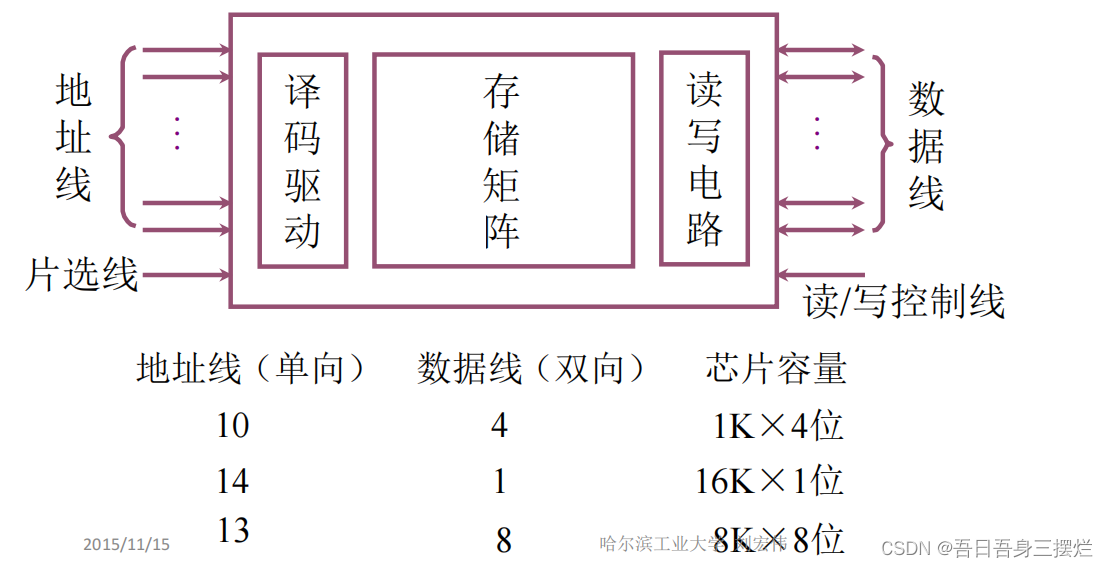

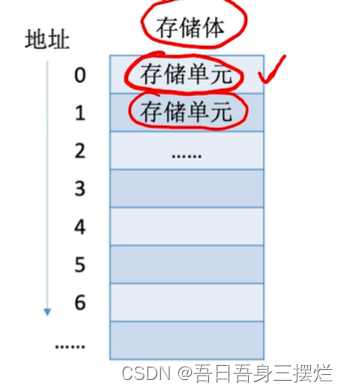

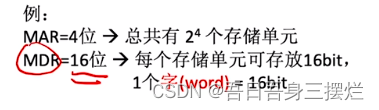

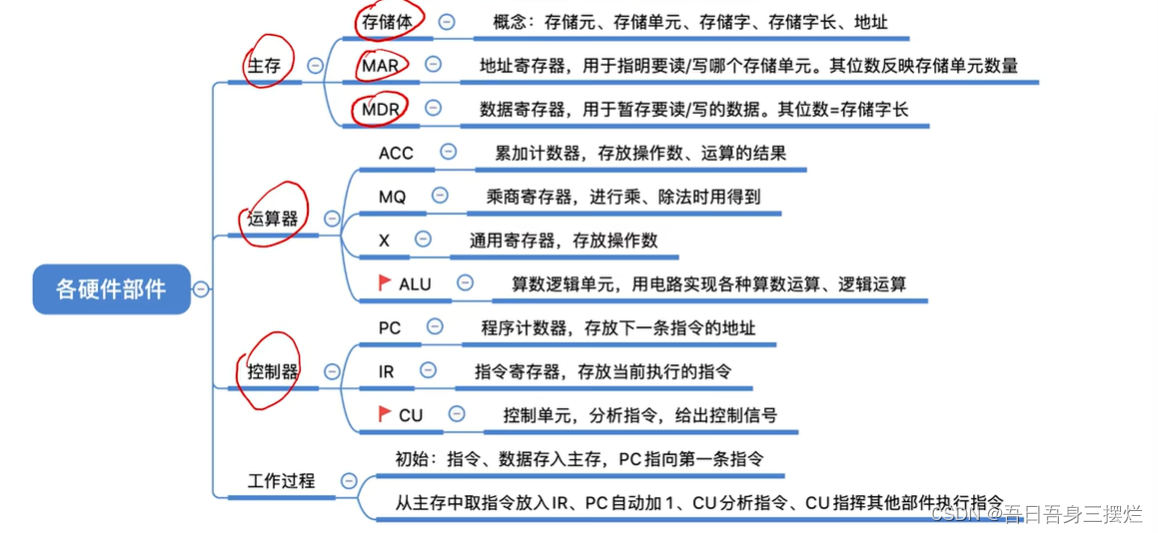

主存储器基本构成:

存储器:数据在存储器内按照地址存储

存储单元:每个存储单元存放一串二进制代码

存储字:存储单元中二进制代码的组合

存储字长:存储单元中二进制代码的位数

存储元:即存储二进制的电元件(电容),每个存储元可以存储1bit

(一个字节有八个比特位,但是一个字有的比特位并不是固定的,具体要看计算机硬件是如何设计的)

(一个字节有八个比特位,但是一个字有的比特位并不是固定的,具体要看计算机硬件是如何设计的)

同时需要注意的是1B=1个字节,1b=1bit

运算器的基本组成:

ACC:

累加器(寄存器),用于存放操作数,或运算结果。

MQ:

乘商寄存器,在乘、除运算时,用于存放操作数或运算结果。.

X:

通用的操作数寄存器,用于存放操作数

ALU:

算术逻辑单元,通过内部复杂的电路实现算数运算、逻辑运算

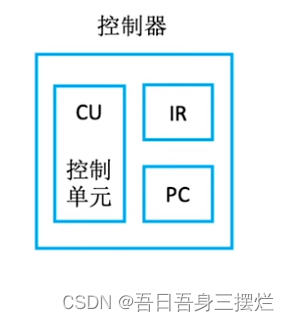

控制器的基本组成:

CU:控制单元,分析指令,给出控制信号

IR:指令寄存器,存放当前执行的指令

PC:程序计数器,存放下一条指令地址,有自动加1功能

(MAR MDR 在现代计算机会集成在cpo内)

一、系统总线

什么要用总线:减少各部件之间的连接线;方便系统的构成、扩充或更新---各部件和总线采用挂接形式,增加一个部件或去掉一个部 件对整个系统的结构不会造成什么影响。

什么是总线:总线是连接各个部件的信息传输线 是 各个部件共享的传输介质

总线的功能:沟通计算机各部件信息传递,并使不同 厂商提供的产品能互换组合

总线标准: 总线标准是系统与各模块、模块与模块之间的一个互连的标 准界面。 总线标准规范: 机械结构规范:确定模板尺寸、总线插头,边沿连接器 等的规格及位置。 功能规范:确定各引脚的名称、定义、功能与逻辑关系。 电气规范:规定信号工作时的高低电平、动态转换时间、 负载能力以及最大额定值。

二、总线的分类

1.片内总线 芯片内部 的总线

2.系统总线 计算机各部件之间 的信息传输线

3.通信总线(外部总线、 I/O 总线):用于 计算机系统之间 或 计算机系统 与其他系统(如控制仪表、移动通信等) 之间的通信

三、浮点表示

浮点数表示法是一种计算机数据表示方法,其中小数点位置可以浮动,不固定在某一位置。在浮点数中,数N可以表示为N=S×r^j,其中S称为尾数,r称为阶,j称为阶。

在科学计数法中,浮点数由符号位、有效数字、指数三部分组成。符号位表示数的正负,有效数字即尾数,指数即阶码。尾数通常是一个纯小数,阶码是一个整数。阶码的符号表示小数点浮动的方向,阶码为正时,表示小数点右移阶码位;阶码为负时,表示小数点左移阶码位。

在计算机中,浮点数通常被表示成如下格式:MsEM,其中M是尾数的符号位,即浮点数的符号位,安排在最高一位;E是阶码,紧跟在符号位之后,占用m位,含阶码的一位符号;M是尾数,在低位部分,占用n位。

在IEEE标准中,浮点数是将特定长度的连续字节的所有二进制位分割为特定宽度的符号域,指数域和尾数域三个域,其中保存的值分别用于表示给定二进制浮点数中的符号,指数和尾数。

此外,浮点数的表示范围比定点数的表示范围大得多。

四、加减法运算

1. 补码加减运算公式

(1) 加法 整数 [A]补+ [B]补= [A+B]补(mod 2n+1)

小数 [A]补+ [B]补= [A+B]补(mod 2)

(2) 减法

A–B = A+(–B )

整数 [A – B]补= [A+(–B )]补= [A]补 + [– B]补 (mod 2n+1)

小数 [A – B]补= [A+(–B )]补 = [A]补 + [– B]补 (mod 2)

连同符号位一起相加,符号位产生的进位自然丢掉

五、存储器