提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 前言

- 一、pandas是什么?

- 二、使用步骤

- 1.引入库

- 2.读入数据

- 总结

前言

这是B站傅里叶的猫视频的笔记

一、建立工程

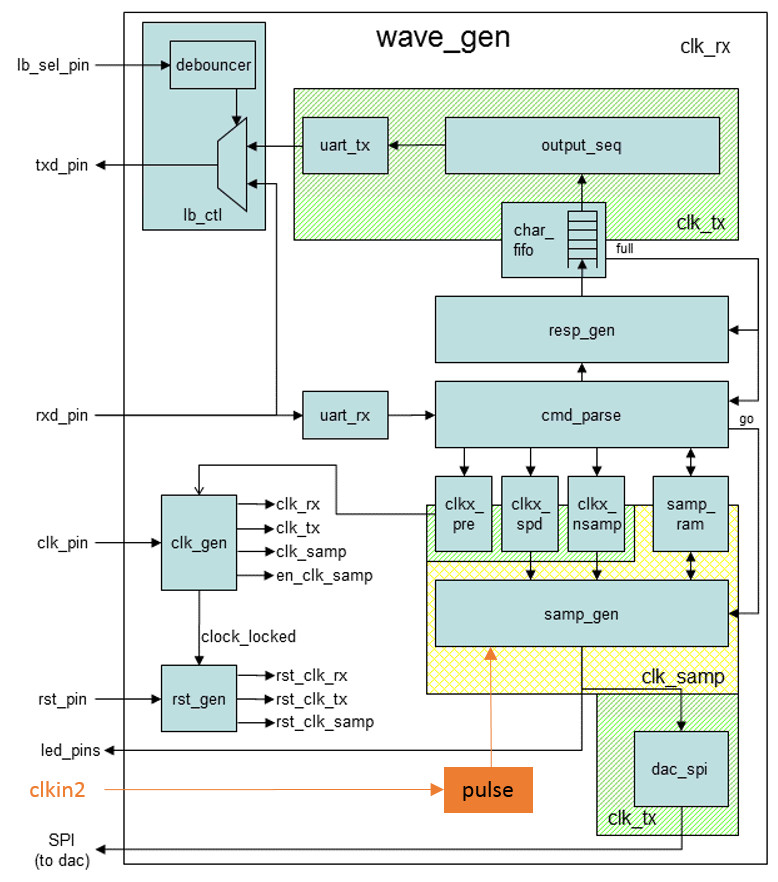

以Vivado的wave_gen为例子。为了引入异步时钟域,我们在此程序上由增加了另一个时钟--clkin2,该时钟产生脉冲信号pulse,samp_gen中在pulse为高时才产生信号。

二、梳理时钟树

我们首先要做的就是梳理时钟树,就是工程中用到了哪些时钟,各个时钟之间的关系又是什么样的,如果自己都没有把时钟关系理清楚,不要指望综合工具会把所有问题暴露出来。

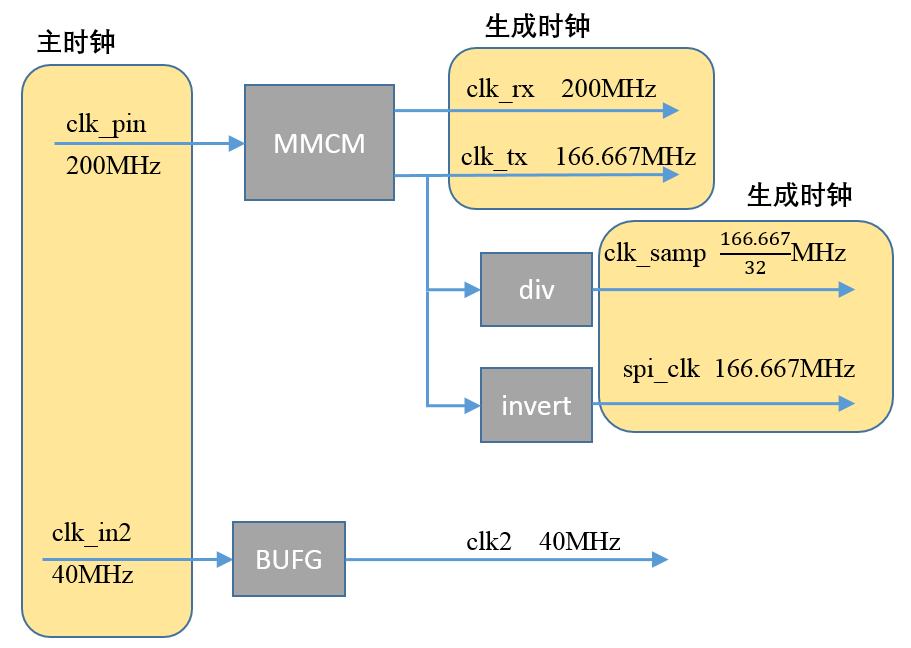

在我们这个工程中,有两个主时钟,四个衍生时钟,如下图所示。

主时钟是FPGA设计中最顶层的时钟源,通常由以下两种方式提供:

-

外部时钟源:通过FPGA的专用时钟引脚(如全局时钟输入引脚)输入,例如晶振、时钟发生器芯片等。

-

FPGA内部固定时钟:少数FPGA内置的固定频率时钟(如某些器件的片上振荡器)。

关键特性

-

无需依赖其他时钟:主时钟是设计的根时钟,其周期和边沿由物理硬件直接决定。

-

全局性:通常通过全局时钟网络(Global Clock Buffer,如BUFG)分配到整个芯片,以降低抖动和偏斜(Skew)。

-

约束语法示例(XDC格式):

create_clock -name sys_clk -period 10 [get_ports CLK_IN]这里

CLK_IN是外部时钟输入引脚,周期为10ns。

衍生时钟

是通过主时钟或其他衍生时钟经过FPGA内部逻辑(如分频、倍频、相位调整)生成的时钟信号。常见的生成方式包括:

-

分频/倍频:通过PLL(锁相环)、MMCM(混合模式时钟管理器)或寄存器分频(如计数器)产生。

-

例如:主时钟100MHz → 通过PLL生成50MHz时钟。

-

-

门控时钟:通过逻辑门(如与门)使能/禁用时钟(需谨慎使用,易导致时序问题)。

-

相位偏移:通过时钟管理单元调整相位(如90°相移时钟)。

关键特性

-

依赖主时钟:衍生时钟的时序必须相对于其父时钟(主时钟或其他衍生时钟)进行约束。

-

需显式定义:工具无法自动识别衍生时钟,必须手动约束。

-

约束语法示例:

create_generated_clock -name clk_div2 -source [get_pins PLL/CLKOUT] -divide_by 2 [get_pins DIV_REG/Q]这里从PLL的输出时钟(

CLKOUT)分频2倍,生成clk_div2。

实际应用注意事项

-

避免衍生时钟的衍生时钟:过度嵌套会增加时序复杂性,建议扁平化时钟结构。

-

谨慎使用组合逻辑生成时钟:可能导致毛刺,推荐使用专用时钟管理单元(PLL/MMCM)。

-

验证时钟关系:通过

report_clocks命令检查时钟树是否按预期约束。

确定了主时钟和衍生时钟后,再看各个时钟是否有交互,即clka产生的数据是否在clkb的时钟域中被使用。

这个工程比较简单,只有两组时钟之间有交互,即:

-

clk_rx与clk_tx -

clk_samp与clk2

其中,clk_rx和clk_tx都是从同一个MMCM输出的,两个频率虽然不同,但他们却是同步的时钟,因此他们都是从同一个时钟分频得到(可以在Clock Wizard的Port Renaming中看到VCO Freq的大小),因此它们之间需要用set_false_path来约束;而clk_samp和clk2是两个异步时钟,需要用asynchronous来约束。