开坑原因

最近开始做实验,实验室的主控采用的是F2812+FPGA,属于够用但不好用的状态。FPGA用于生成调制信号,DSP完成采样和控制。师兄师姐研究拓扑及调制策略,对驱动数量以及驱动逻辑有比较高的要求,因此不好脱离FPGA,只能继续使用F2812+FPGA的平台。我研究控制算法,F2812只能定点运算,使得写代码变得繁琐。于是硬着头皮开始自己搭28335的主控平台(28335也比较老了)。其实28335比较简单,跟之前用ARM差不多。只是需要一个人搭建完成一个完整的控制框架有点孤独,遇到问题也没法讨论~

为什么又要继续开坑F28379呢?

(1) 中断时间不够

因为最近又发现中断频率10kHz(其实也不高)的情况下,中断时间捉襟见肘,需要时刻注意中断时间是否充足。实验室已有的方案中,三电平逆变器的SVPWM调制策略在FPGA中完成,而我目前的方案是也在这10kHz的中断中完成,又进一步压缩了其他程序可使用的时间。

(2) CCS Debug易掉线

做并网实验时,电压等级上升后,合并网开关时容易导致CCS Debug断开,随后程序跑飞。那么就需要断开DSP与PC的连接。我的实验需求又需要在线的调节参数,因此计划通过串口实现。串口收发数据增加了中断处理的压力。

(3) DA输出

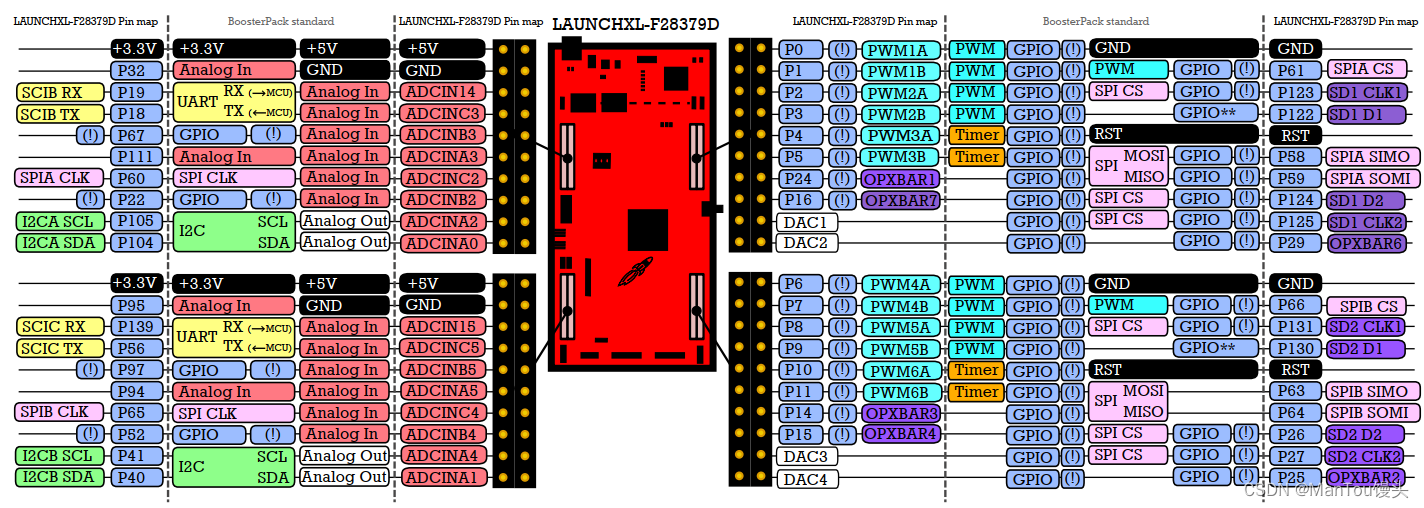

在实验计划中,需要开展暂态实验,要求示波器能够观察相角,则需要DAC模块,28379的LAUNCHPAD板载了4路PWM-DAC应该能够满足需求。

(4) 28379D性能更优秀

28379的主频更高,程序处理更快。双核+双CLA使得处理程序更加的从容。

开坑目标

F28379D的最终目标是:

Core1 的任务

(1)ADC采集;(2)DAC输出;(3)串口发送与接收(Vofa+);(4)与Core2通信

Core2 的任务

(1)控制算法;(2)与Core1通信

CLA的任务

(1)SVPWM调制

开坑计划

- CCS 28379D环境搭建

- Core1:GPIO控制

- Core1:ADC采集

- Core1:DAC输出

- Core1:Vofa+串口发送与接收

- Cores:双核通信

- CLA:SVPWM

- Core2:控制算法

- 基于MATLAB/Simulink的MBD(最大的坑,咕咕咕)