高速存储设计会有各种需求的考虑,那么对应的方案也不完全相同,这篇文章出一期纯FPGA实现的高速存储方案。用纯fpga实现高速存储板卡有易国产化,功耗低和体积小等特点,缺点就是灵活性不是很强,实现标准ext4和nfs文件系统会非常难。

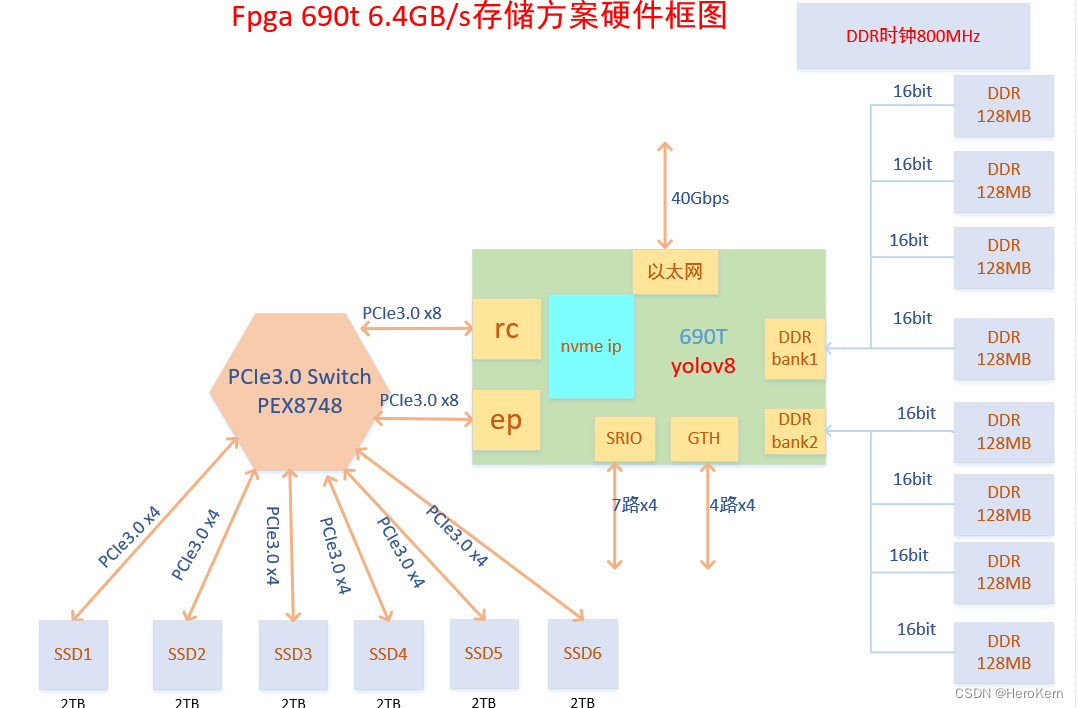

690T高速存储硬件设计框图如下,switch下面挂载6张ssd,一路x8 到fpga host,1路x8到fpga ep,pcie端采用nvme ip实现ssd盘的读写,40Gbps以太网数据,以及多通道的srio和GTX数据,整个架构中最核心的就是nvme ip,nvme ip扮演了大脑的角色,负责枚举ssd,分配地址,以及nvme协议处理等。

该方案可移植性很强,如果需要更高的速度,仅仅需要将pcie switch下面挂接更多的ssd,如果port不够可以挂更多的pcie switch,因为switch 与fpga之间有两路pcie3.0 x8,那么就最大的下盘速率大约有16GB/s,具体跑多少速度挂载多少ssd,需要结合成功案例经验在做决定。

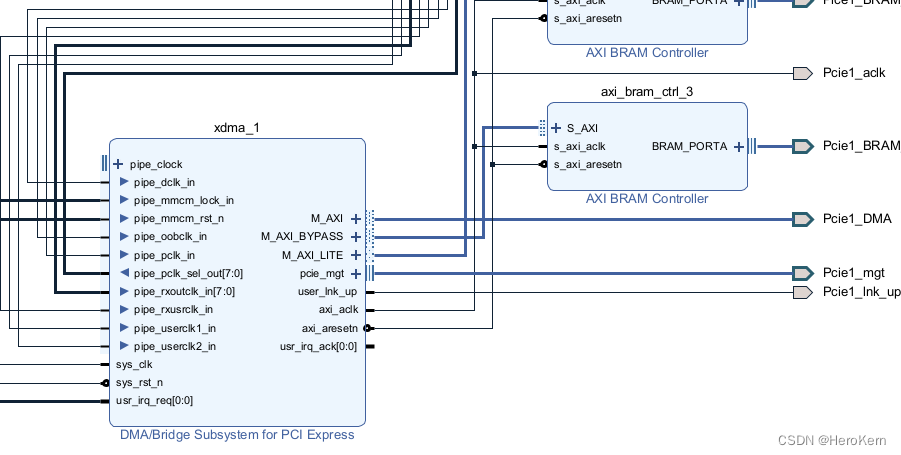

在选型Pcie 核690t有很大的优势,支持多个pcie硬核,所以不用担心没得软核啦,比如下图就是xdma作为ep的配置。

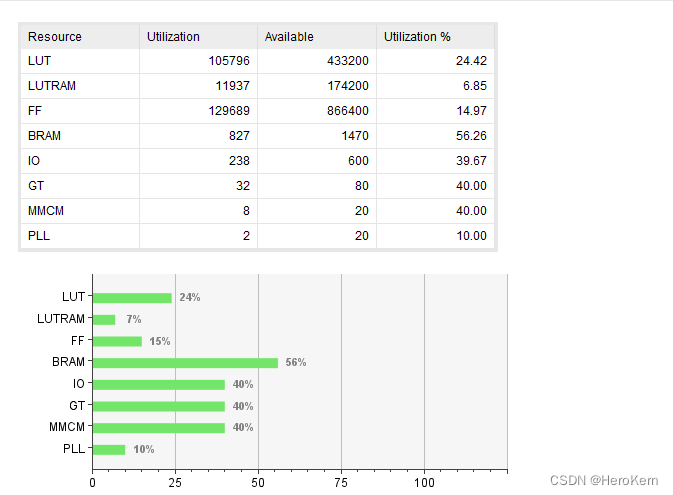

关于nvme ip资源消耗情况,目前高速存储使用的资源如下(外部接口没有全部使用),其实代码中有个细节可以优化很多bram接口,因为前期设计考虑冗余了,导致资源消耗过多。

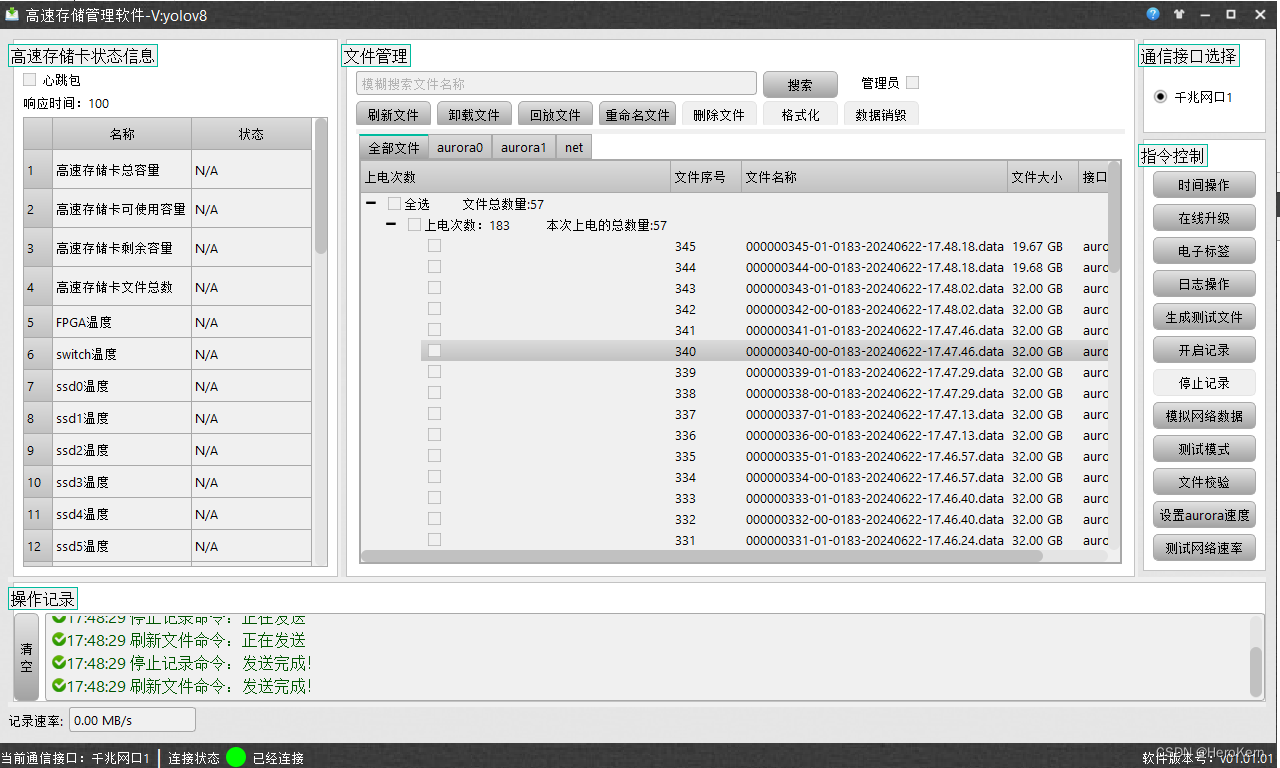

在690t中实现tcp协议并且与上位机通讯。

nvme ip支持如下IO命令

管理命令:

identify

set feature

abort cmd

creat sq cmd

creat cq cmd

fortmat nvm cmd

IO命令

read/write cmd

flush cache cmd ###异常掉电可以下发该命令告知SSD将缓存中的数据program到nand flash

trim cmd #该命令在格式化使用