文章目录

- 3 算术运算和逻辑运算

- 3.1 二进制数运算方法

- 3.2 逻辑代数的基本运算与逻辑表达式化简

- 4. 计算机组成及工作原理

- 4.1 CPU的组成与工作原理

- 4.1.1 运算器(数据加工中心)

- 4.1.2 控制器(指令指挥中心)

- 4.1.3 计算机指令

- 4.1.4 寻址方式

- 4.1.5 计算机流水线

- 4.2 常用I/O设备、通信设备的性能以及基本工作原理

- 4.2.1 输入设备

- 4.2.2 输出设备

- 4.2.3 存储设备

- 4.2.4 通信设备

- 4.3 I/O接口的功能、类型和特点

- 4.3.1 I/O接口功能

- 4.3.2 接口类型

3 算术运算和逻辑运算

3.1 二进制数运算方法

略,二进制的基本加减乘除和十进制没什么区别,没啥好说的。

3.2 逻辑代数的基本运算与逻辑表达式化简

- 逻辑代数基本运算如下表:

| 运算 | 符号 | 真值表 | 逻辑表达式 |

|---|---|---|---|

| 与(AND) | · 或 ∧ | 0·0=0, 0·1=0, 1·1=1 | Y = A·B |

| 或(OR) | + 或 ∨ | 0+0=0, 0+1=1, 1+1=1 | Y = A+B |

| 非(NOT) | ¬ 或 ¯ | ¬0=1, ¬1=0 | Y = ¬A |

| 异或(XOR) | ⊕ | 0⊕0=0, 0⊕1=1, 1⊕0=1, 1⊕1=0 | Y = A⊕B |

- 位运算说明如下表:

| 运算符 | 功能 | 示例 |

|---|---|---|

& | 按位与 | 1010 & 1100 = 1000 |

| | 按位或 | 1010 | 1100 = 1110 |

^ | 按位异或 | 1010 ^ 1100 = 0110 |

~ | 按位取反 | ~1010 = 0101 |

<< | 左移(高位丢弃,低位补0) | 1010 << 2 = 101000 |

>> | 右移(低位丢弃,高位补符号位) | 1010 >> 2 = 0010 |

-

逻辑表达式化简

- 交换律:

A+B = B+A,A·B = B·A - 结合律:

(A+B)+C = A+(B+C) - 分配律:

A·(B+C) = A·B + A·C - 恒等率:消除无效操作,如

×1或+0 - 吸收率:消除冗余操作,如

A + (A · B) = A或A · (A + B) = A或A + (¬A · B) = A + B - 德摩根定律:

¬(A+B) = ¬A·¬B,¬(A·B) = ¬A + ¬B

- 交换律:

-

化简方法

-

代数法:应用逻辑定律逐步化简

原始式:Y = A·B + A·¬B + ¬A·B 化简: = A·(B + ¬B) + ¬A·B (分配律) = A·1 + ¬A·B (互补律:B + ¬B = 1) = A + ¬A·B (恒等律:A·1=A) = A + B (吸收律:A + (¬A · B) = A + B) -

卡诺图法(K-map):

- 这个方法很复杂,其大概步骤如下:

- 将真值表转换为方格图(变量数≤4)

- 圈出相邻的

1(必须为2ⁿ个) - 消去变化变量,保留恒定变量

- 这个方法很复杂,其大概步骤如下:

具体过程可以参考下这个视频,真的很复杂😭。。

-

4. 计算机组成及工作原理

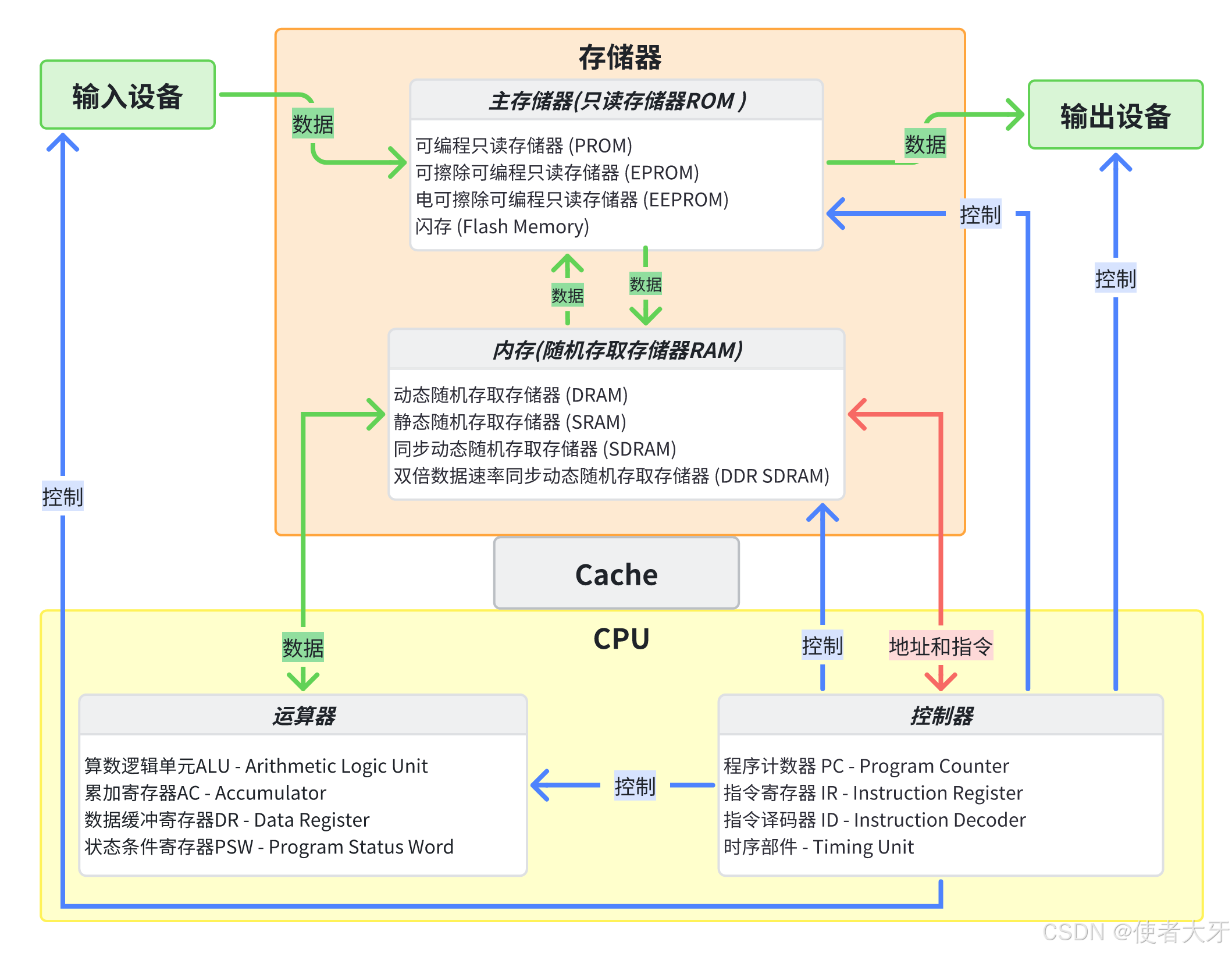

计算机系统的基本架构可以由下面的框图简单表示:

4.1 CPU的组成与工作原理

CPU由运算器和控制器两大模块组成:

4.1.1 运算器(数据加工中心)

| 组件 | 功能说明 | 工作流程示例 |

|---|---|---|

| 算术逻辑单元(ALU) | 执行所有算术(±*/)和逻辑运算(AND/OR/NOT) | 从寄存器取操作数 → 运算 → 结果回写 |

| 累加寄存器(AC) | 为ALU提供临时工作区,存储中间结果 | AC ← AC + DR(累加操作) |

| 数据缓冲寄存器(DR) | 暂存来自内存的指令或数据,缓解CPU与内存速度差异 | 取指令阶段:DR ← Memory[PC] |

| 状态寄存器(PSW) | 存储运算状态标志(零标志ZF/进位CF/溢出OF等) | ALU运算后自动更新PSW |

4.1.2 控制器(指令指挥中心)

| 组件 | 功能说明 | 工作流程示例 |

|---|---|---|

| 程序计数器(PC) | 存储下一条指令的内存地址,自动递增或跳转 | PC ← PC + 1(顺序执行) |

| 指令寄存器(IR) | 保存当前正在执行的指令 | IR ← DR(取指令阶段) |

| 指令译码器(ID) | 解析指令操作码,生成控制信号 | 识别MOV AX,BX→ 激活数据通路控制信号 |

| 时序部件 | 生成时钟信号,协调各部件工作节奏 | 发出取指/执行/写回三阶段时序脉冲 |

4.1.3 计算机指令

指令的本质是机器语言语句,CPU直接执行的二进制代码 ,其格式如下:

| 字段 | 作用 | 示例场景(加法指令) |

|---|---|---|

| 操作码(OP) | “做什么”:指明操作类型(如加减/跳转/存储) | ADD → 算术加法 |

| 地址码(Aₙ) | “对谁做”:提供操作数地址或结果存储位置(数量因指令类型而异) | A₁=源数据1, A₂=源数据2, A₃=目标地址 |

4.1.4 寻址方式

①立即寻址

- 特点:操作数直接包含在指令中

- 格式:

OP + 操作数 - 示例:

MOV AX, 5(将数值5直接存入AX寄存器) - 优点:执行速度快(无需访问内存)

- 缺点:操作数无法修改,灵活性低

②直接寻址

- 特点:指令中存放操作数的内存地址

- 格式:

OP + 内存地址 - 示例:

MOV AX, [1000H](将内存地址1000H处的内容存入AX) - 优点:访问确定的内存位置

- 缺点:地址长度限制指令长度

③间接寻址

- 特点:指令中的地址指向另一个地址(指针的指针)

- 格式:

OP + 地址指针 - 示例:

MOV AX, [[BX]](BX寄存器的值作为地址,再取该地址的内容) - 优点:支持动态内存访问

- 缺点:需要两次内存访问,速度慢

④寄存器寻址

- 特点:操作数存放在寄存器中

- 格式:

OP + 寄存器名 - 示例:

ADD AX, BX(AX = AX + BX) - 优点:速度最快(CPU内部操作)

- 缺点:寄存器数量有限

⑤寄存器间接寻址

- 特点:寄存器中存放的是操作数的地址

- 格式:

OP + 寄存器名 - 示例:

MOV AX, [BX](BX的值作为内存地址,取该地址内容到AX) - 优点:比内存间接寻址更快

- 缺点:仍需要一次内存访问

寻址方式对比

| 寻址方式 | 操作数位置 | 访问次数 | 速度 | 灵活性 |

|---|---|---|---|---|

| 立即寻址 | 指令内部 | 0 | ★★★★★ | ★★ |

| 寄存器寻址 | 寄存器 | 0 | ★★★★★ | ★★★ |

| 直接寻址 | 指定内存地址 | 1 | ★★★ | ★★★★ |

| 寄存器间接寻址 | 寄存器指向的内存 | 1 | ★★★★ | ★★★★★ |

| 间接寻址 | 内存指向的内存 | 2 | ★★ | ★★★★★ |

典型应用场景

- 立即寻址:初始化常量(如

MOV CX, 10) - 寄存器寻址:高速数据运算(如

ADD DX, SI) - 直接寻址:访问固定内存变量(如

MOV AL, [VAR1]) - 寄存器间接寻址:数组/字符串处理(如

MOV AL, [SI]配合SI递增) - 间接寻址:指针操作(如C语言中的双重指针

**p)

4.1.5 计算机流水线

流水线的核心思想是将指令执行过程分解为以下多个阶段,各阶段并行处理不同指令,类似工厂流水线:

- 取指:从内存读取指令

- 分析:解析指令操作

- 执行:ALU执行运算

- 访存:访问内存数据

- 写回:将结果写回寄存器

时钟周期 → 1 2 3 4 5 6 7 ...指令1: 取指 分析 执行 访存 写回指令2: 取指 分析 执行 访存 写回指令3: 取指 分析 执行 访存 写回

关键参数:

- 流水线周期(Δt):耗时最长的阶段所需时间(决定流水线速度)

- 吞吐率(TP):单位时间内完成的指令数(TP = 指令数n / 总时间Tₖ)

流水线时间计算:

-

理论公式(更精确):

T 总 = t 1 + t 2 + … + t k + ( n − 1 ) × Δ t T_{\text{总}} = t_1 + t_2 + \ldots + t_k + (n-1) \times \Delta t T总=t1+t2+…+tk+(n−1)×Δt

(k=阶段数,n=指令数) -

简化公式(常用):

T 总 = k × Δ t + ( n − 1 ) × Δ t T_{\text{总}} = k \times \Delta t + (n-1) \times \Delta t T总=k×Δt+(n−1)×Δt

(假设所有阶段时间=Δt)

示例计算:

题目:每条指令分为3个阶段:取指2ns,分析2ns,执行1ns,执行100条指令

-

流水线周期Δt = 最长阶段时间 = 2ns

-

总时间 = (3阶段×2ns) + (99×2ns) = 6 + 198 = 204ns

-

实际吞吐率:

T P = n T 总 = 100 204 ns ≈ 0.49 条/ns TP = \frac{n}{T_{\text{总}}} = \frac{100}{204\text{ns}} ≈ 0.49 \text{条/ns} TP=T总n=204ns100≈0.49条/ns -

最大吞吐率:

T P max = 1 Δ t = 1 2 ns = 0.5 条/ns TP_{\text{max}} = \frac{1}{\Delta t} = \frac{1}{2\text{ns}} = 0.5 \text{条/ns} TPmax=Δt1=2ns1=0.5条/ns

4.2 常用I/O设备、通信设备的性能以及基本工作原理

4.2.1 输入设备

| 设备 | 性能指标 | 工作原理 | 应用场景 |

|---|---|---|---|

| 键盘 | 按键寿命、响应延迟 | 扫描矩阵电路检测按键通断,生成扫描码 | 人机交互 |

| 鼠标 | DPI(精度)、采样率 | 光学传感器捕捉位移,编码为坐标数据 | 图形界面操作 |

| 扫描仪 | 分辨率(DPI)、色彩深度 | CCD/CMOS传感器逐行扫描光反射信号 | 文档数字化 |

4.2.2 输出设备

| 设备 | 性能指标 | 工作原理 | 特点 |

|---|---|---|---|

| 显示器 | 分辨率、刷新率、色域 | LCD:液晶分子偏转控制透光 OLED:有机发光二极管自发光 | 响应时间影响动态画面 |

| 打印机 | PPM(页/分钟)、打印精度 | 激光打印机:静电吸附碳粉 喷墨打印机:微滴喷射 | 激光机适合大批量打印 |

4.2.3 存储设备

| 设备 | 性能指标 | 工作原理 | 关键参数 |

|---|---|---|---|

| 机械硬盘 | 转速(7200/10000RPM)、寻道时间 | 磁头在盘片磁性介质上读写数据 | 延迟受物理运动限制 |

| 固态硬盘 | 读写速度(MB/s)、IOPS | NAND闪存芯片电子存储,无机械部件 | 抗震动、低功耗 |

4.2.4 通信设备

| 设备 | 性能指标 | 工作原理 | 协议标准 |

|---|---|---|---|

| 网卡 | 速率(1Gbps/10Gbps)、MAC地址 | 将数据封装为帧,处理物理层信号调制 | IEEE 802.3(以太网) |

| 调制解调器 | 调制速率(56Kbps等) | 数字信号↔模拟信号转换(ADSL使用频分复用) | V.34/V.90标准 |

4.3 I/O接口的功能、类型和特点

4.3.1 I/O接口功能

- 数据缓冲:解决速度不匹配

- 信号转换:电平/格式转换

- 设备选择:地址译码

- 命令译码:解释CPU命令

- 状态反馈:返回设备状态

4.3.2 接口类型

| 类型 | 特点 | 典型应用 | 传输方式 |

|---|---|---|---|

| 并行接口 | 多线同时传输(如8/16位),速度快但易干扰(IEEE 1284) | 老式打印机 | 并行 |

| 串行接口 | 单线逐位传输,抗干扰强(USB 3.0可达5Gbps) | 鼠标、键盘、移动存储 | 串行 |

| DMA接口 | 直接内存访问,不经过CPU(通过DMA控制器) | 高速磁盘传输 | 总线主控 |

| SCSI | 支持多设备菊链连接,高可靠性 | 企业级存储阵列 | 并行/串行 |