13.RFSoC SDR的设计工具和工作流程

13.1 高层次设计过程

RFSoC器件分为两个主要的可定制部分,处理系统(PS)和可编程逻辑(PL)。在为RFSoC设计系统时,值得首先考虑的是设计的功能如何在这两个元素之间进行划分。例如,数据是在PS上生成或处理,还是只在PL上执行。这种划分是设计过程中的第一步。

此外,虽然强化的RFDC和SD-FEC IP核与PL集成,但可以通过接口端口从PL和PS控制它们,并使用软件驱动程序。对于某些设计,如果延迟是一个关键问题,那么从PL配置这些IP核可能是可取的。然而,对于无线电可能需要定期重新配置的SDR设计,最好在PS上使用软件驱动程序。

作为本书后面介绍的设计的预览(第16章和Notebook Set I中的OFDM收发器),我们考虑其功能如何在PS和PL之间划分。收发器包含发送器和接收器处理,以及用于演示目的的附加功能。发射器产生随机数据,然后将该数据转换为OFDM信号,然后将其发送到RF-DAC。接收器执行相反的过程,从RF-ADC接收数据,进行OFDM接收处理,并恢复数据。发送器和接收器逻辑都需要允许配置更改的控制输入。此外,在传输和接收路径上的不同点截取数据以供检查。

作为本书后面介绍的设计的预览(第16章和Notebook Set I中的OFDM收发器),我们考虑其功能如何在PS和PL之间划分。收发器包含发送器和接收器处理,以及用于演示目的的附加功能。发射器产生随机数据,然后将该数据转换为OFDM信号,然后将其发送到RF-DAC。接收器执行相反的过程,从RF-ADC接收数据,进行OFDM接收处理,并恢复数据。发送器和接收器逻辑都需要允许配置更改的控制输入。

本章的其余部分将介绍用于开发PL和PS系统的各种软件工具和设计方法。我们还详细介绍了我们用于开发本书中许多设计的设计流程。

13.2 PL设计

RFSoC系列中的所有第1、2和3代器件都具有一组标准化的FPGA资源,其中包括clb和DSP48E2片,以及Block ram和Ultra ram形式的内存。这些资源可以由用户完全重新配置,支持各种各样的应用程序和用例——对于SDR设计,PL在实现信号处理算法方面特别强大。

除了逻辑结构外,RFSoC器件还具有强化资源,如SD-FEC块和RF数据转换器,。这些强化块提供了计算密集型功能的优化实现,控制其操作的参数可以重新编程以适应目标应用。对于RFDC,这包括设置采样率,抽取和插值率。这些资源可以直接连接到用户配置的PL逻辑结构,以构建复杂的设计,如SDR收发器。

在设计RFSoC系统时,应考虑外部接口,特别是对于ZCU208或RFSoC4x2等评估板。如前所述,外部射频信号可以通过RFDC通过平衡器和SMA传输和接收。可能还需要额外的IO,例如支持外部显示、高速QSFP数据卸载或Pmod接口。这些外部IO接口通过PL内的可重构连接器启用,并提供了将RFSoC集成为更大系统的一部分的巨大潜力(例如,包括SDR功能以及其他功能)。

本节的其余部分将回顾用于开发基于RFSoC的SDR系统的硬件设计的设计工具和过程。采用自顶向下的方法:我们首先考虑系统级设计,然后回顾创建构成设计层次结构较低层次的IP块的方法。

13.2.1 Vivado IP集成器

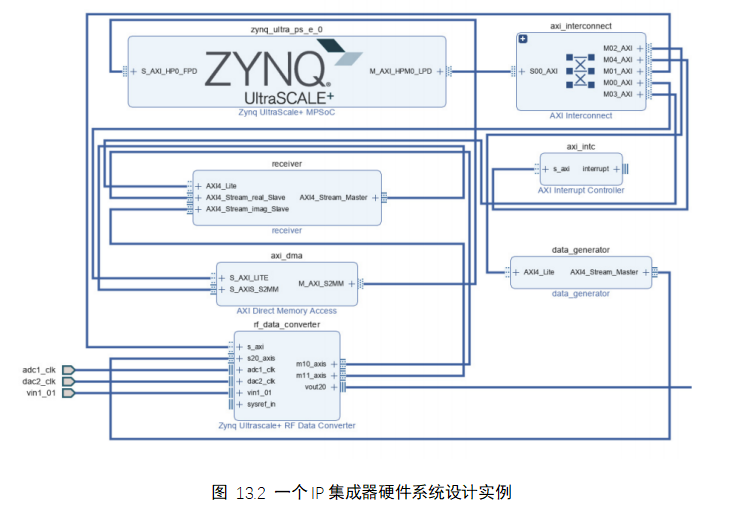

将自定义硬件逻辑、预先存在的IP内核和IO合并在一起的最有效方法是通过IP Integrator (IPI),这是AMD的Vivado集成开发环境(IDE)的一部分。可以使用IPI GUI(如图13.2所示)或通过工具命令语言(Tcl)脚本对预生成的IP核进行实例化并连接以形成块设计。

IPI设计通常通过接口组合IP核的实例来构建,即共享公共功能的信号组。使用接口进行设计的主要好处是减少了复杂性——工具中的单个图形连接可以表示一组信号和总线。如果这些信号和总线都是可视化的,并且必须独立连接,那么设计的复杂性、工作量和时间就会大得多。通过使用接口,在IPI GUI中建立一个连接,或者相当于一个Tcl命令,就可以在IP核和系统设计中的另一个组件之间创建完整的连接。

使用接口进行设计还可以使用IPI设计规则检查(DRCs),它知道特定接口类型所需的信号,因此可以提供信号正确连接的验证。这些检查在设计组装时实时发生,并且可以与编程语言中的语法错误消息进行比较。

如果创建一个针对特定评估平台的Vivado项目(例如ZCU208 RFSoC开发板),那么IP Integrator具有适用的外部FPGA引脚的知识。这允许利用IPI连接自动化功能将设计的IO端口绑定到板的外部引脚,从而节省设计师的精力。通过此过程自动创建适当的物理引脚和时钟约束。IP Integrator还自动创建一个顶级包装器文件,该文件用硬件描述语言(HDL)代码描述了整个系统的接口。

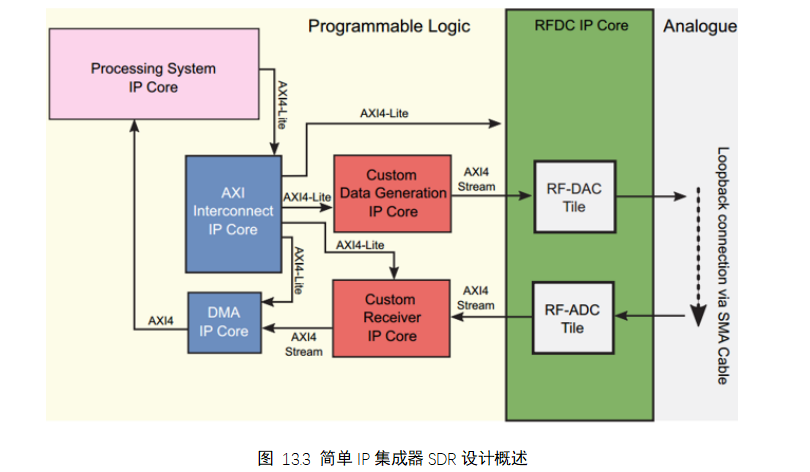

一个概念性IP Integrator设计如图13.3所示。该设计代表了RFSoC环回测试配置(其中RF - DAC的输出通过SMA电缆和模拟滤波器直接连接到同一设备的RF-ADC输入)。一个概念性IP Integrator设计如图13.3所示。该设计代表了RFSoC环回测试配置(其中RF - DAC的输出通过SMA电缆和模拟滤波器直接连接到同一设备的RF-ADC输入)。

本设计突出了RFSoC IP集成器设计的一个关键特征——处理系统IP核——它代表了器件的PS部分。在这个IP核中有许多可配置的选项,包括:IO选项,如SPI和I2C;各种时钟选项,包括外围时钟和PL时钟;和可配置内存,如DDR4。

13.2.2 IP集成器的AXI接口

在使用IP集成器进行设计时,关键的接口类型之一是AXI协议,它用于连接需要高带宽、低延迟通信的处理元素和IP核。RFSoC设备在PL和PS中实现了该标准的第四次迭代(AXI4),并且有三种关键类型的AXI4总线可用于RFSoC设计:AXI4, AXI4-lite(都用于内存映射接口)和AXI4-stream(用于点对点数据传输)。IP核通过从接口和主接口由AXI4总线连接。AXI4总线中的每个独立通道都由一组信息信号以及提供双向握手机制的有效信号和有效信号组成。

我们可以在图13.3中看到axis4协议的用法。具体来说,有:IP核之间的AXI4-Stream接口;ax4 - lite接口连接从PS到PL IP核,通过一个AXI互连IP核;以及用于以高吞吐率将数据从PL传递到PS的AXI DMA IP核。在外部软件中设计自定义IP核时,可以将端口指定为三种AXI4总线类型中的任何一种,并将IO端口指定为从接口或主接口。下面更详细地描述了每种AXI4类型的典型用法。

AXI4——该协议用于需要在处理元素(RFSoC PS)和IP内核之间的内存映射链接的连接。它能够单拍传输或突发传输,每次传输多达256个数据拍,数据可以同时双向移动。AXI4有五个独立的通道:读地址、读数据、写地址、写数据和写响应。每个通道都有用于传输数据的专用资源。该协议适用于向主存和从主存之间传输大量数据——PS中的大数据块可以通过每个最多256个数据元素的多个突发传输到PL——并且可以在使用AXI4直接内存访问IP核的IPI设计中实现。

AXI4-lite——一个简单的内存映射链接,减少了握手信号,导致比完整的AXI4更低的资源分配。AXI4- lite与AXI4共享相同的5个通道。AXI4和AXI4- lite之间的主要区别在于后者只支持单拍传输,而不支持AXI4支持的突发传输。该协议通常用于低带宽通信,例如与IP核和处理元素的控制寄存器,通常来自基于PS的IP驱动程序。

AXI4-Stream——AXI4-Stream支持点对点数据流。它提供不受限制大小的突发传输。不需要地址通道,因为该协议的用例是设备内源和目标IP核之间的直接数据流。因此,AXI4 -stream协议对于视频、通信和网络应用中的信号处理特别有用,并且是用于向RFSoC设备的RFDC传输数据和从RFDC传输数据的方法。

13.2.3 IP核心和库

Vivado允许使用IP核来帮助硬件设计的开发。IP核是一个独立的硬件块,相当于HDL描述,可以集成到系统设计中。IP核通常是高度可参数化的,并存储在IP存储库中,可以根据需要以不同的设计部署它们。AMD提供用于RFDC和SD-FEC模块的IP内核,以及用于DSP和通信的丰富的高价值内核库,可加速SDR硬件设计,以及用于一系列应用的更多IP。

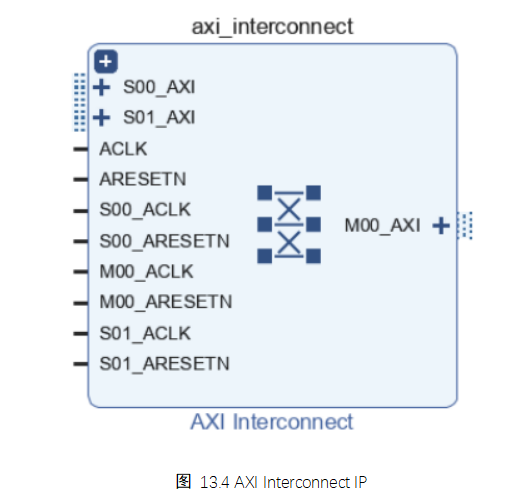

图13.4显示了一个来自Vivado GUI的AXI Interconnect IP核。支持连接到更宽PL设计的IO接口出现在IPI的IP核表示上:该核有两个输入接口S00_AXI和S01_AXI,以及一个输出接口M00_AXI。时钟端口提供了这样的每个这些接口可以独立的时钟。设计师还可以选择设计和包装自己的IP核,并创建自己的存储库。

13.2.4 创建自定义IP的工具和方法

1. HDL代码开发

硬件设计的传统方法是使用两种主要HDL中的一种开发HDL代码,VHDL和Verilog,或SystemVerilog。HDL描述指定了设计的接口和功能,并且通常开发附带的测试台用于验证目的。HDL IP核可以在Vivado IDE中开发和模拟。HDL支持层次结构,使得开发、测试和集成硬件模块以及重用现有模块变得容易。

2. Vitis 高级综合(HLS)

Vitis HLS是一种AMD工具,可以与Vivado一起安装,并支持从C和c++函数开发IP内核。该工具通过使用pragmas 来自动化代码修改,以优化基于C的函数来实现硬件设计目标(例如,最大化数据吞吐量,或最小化延迟)。因此,函数可以作为软件算法进行充分的编译、模拟和调试,然后再合成为IP核。由于Vitis和Vivado之间的紧密集成,设计人员可以轻松地从Vitis HLS中创建与他们的Vivado版本兼容的IP核心存储库。

3. HDL编码器和SoC Blockset

MathWorks HDL Coder是一种基于MATLAB和Simulink环境的硬件设计替代工具。使

用HDL Coder,可以从兼容的MATLAB函数和基于块的Simulink模型中生成HDL代码,以创建适合在Vivado设计中使用的IP核。一个简单的HDL编码器设计示例将在本章后面的图13.17中看到。

HDL Coder的功能可以通过SoC Blockset进行扩展,SoC Blockset为FPGA内存、外部IO和PS调度以及强化的RFSoC资源(如RFDC)添加了Simulink块。这些块也可以生成为HDL代码,从而可以从Simulink生成完整的Vivado块设计。当使用SoC Blockset时,PS和PL元素可以与SoC Builder一起组成一个单一的Simulink模型,这有助于为RFSoC设备创建整个嵌入式系统的软硬件协同设计。

4. Model Comeposer

AMD在Simulink环境中以Vitis Model Composer的形式提供了自己的基于模型的HDL支持。该工具可以与Vivado一起安装,并提供由AMD维护的200多个块,可以从中生成HDL。设计器能够导入自定义块。通过这种方式,IP核可以模拟并导出到包含库块和用户开发块的混合硬件。

Model Composer提供了一组专门为DSP应用设计和优化的支持HDL的模块,包括用于有限脉冲响应滤波器、快速傅里叶变换和基于坐标旋转数字计算机算法的三角运算的模块。这些模块已经针对硬件部署进行了优化,并包括实现选项,允许设计人员根据模块类型针对特定的PL架构资源,如DSP48E2片和RAM块。

5. 开源HDL生成选项

一些可选的HDL和IP核生成选项可以从开源社区获得。Clash是一种高级HDL,它借用了Haskell编程语言的规则和语法,并在编译时映射到VHDL或Verilog。MyHDL和Amaranth都是基于python的项目,采用类似的方法,通过在编译时转换为VHDL或Verilog。Chisel与Vitis HLS相当,它向Scala编程语言添加了支持hdl的实用程序。

13.2.5 Vivado硬件设计

Vivado支持在RFSoC和其他AMD可编程器件上进行编程的硬件设计。整个硬件设计工作流程可以在Vivado中进行。在最底层,Vivado使用HDL来描述将在PL上实现的设计,并且它支持VHDL, Verilog和SystemVerilog语言。设计中所有基于PL的组件都必须包含在HDL描述中,包括外部IO,内存,使用的任何强化资源(如RFDC或SD-FEC块)以及与PS的接口。重要的是要强调,在HDL中完成完整硬件描述的步骤可以使用其他工具和设计方法完成,即设计人员可以在更高的抽象层次上工作。正如本章前面所讨论的,IP Integrator被推荐用于系统设计,并且诸如Vitis HLS, Model Composer或HDL Coder之类的工具可以用于IP创建。

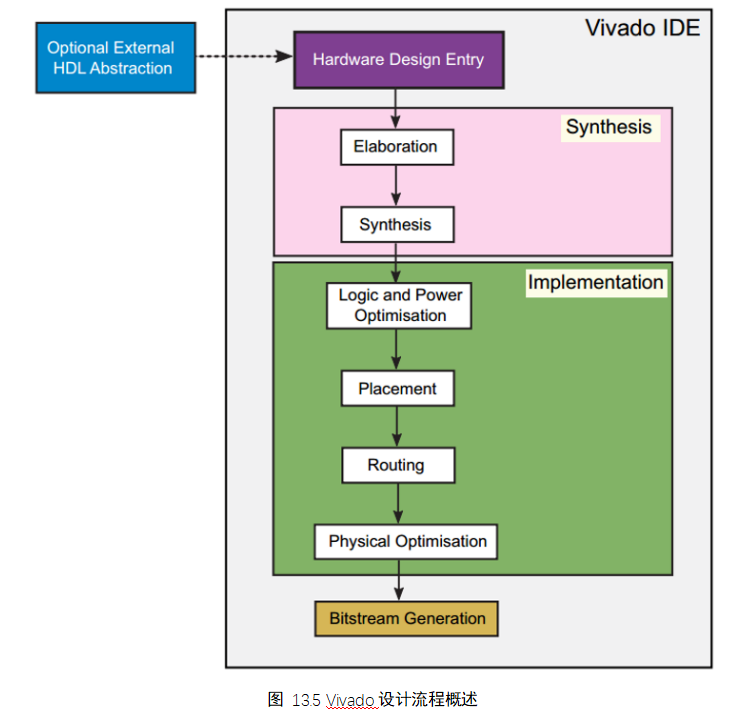

一旦完成了PL设计的HDL描述,就需要一系列进一步的步骤来生成一个编程文件,用它来配置PL和所设计的电路。这被称为硬件设计流程,下面将对其进行概述。

Vivado硬件设计流程如图13.5所示,可以总结如下:

1.使用HDL对硬件设计进行描述。在此阶段进行模拟和测试,以验证预期的功能操作。

2.在综合的第一阶段,解析HDL代码以定位标准逻辑元件的描述。

3.将HDL代码配置为特定于技术的网络列表,将的网络列表所描述的电路映射到目标设备的PL资源

4.在综合之后,执行实施。在基于机器学习的预测指导下,将网表中指定的组件和连接分配给目标设备上的物理逻辑和路由资源。这个过程可以分为几个子步骤:逻辑和功率优化、将网表的单元映射到物理设备资源、网表组件之间的连接分配给目标设备上的物理路由资源、物理优化、生成比特流。

每个进程都可以在Vivado IDE中驱动,也可以通过编程方式驱动。

13.2.6 强化资源的IP核

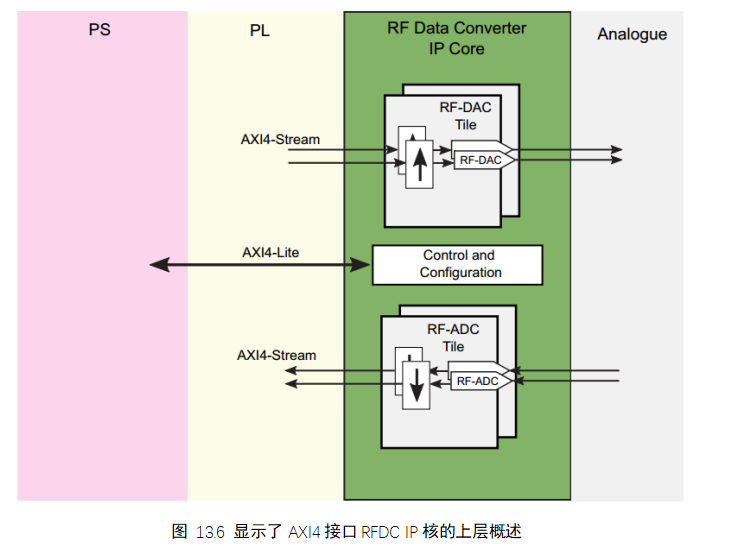

1. 射频数据转换器IP核

图13.6展示了RFDC IP核的架构。IP核内的每个RFDC块都绑定到一个AXI4-Stream接口,每个RF-ADC块连接到一个主接口,每个RF-DAC块连接到一个从接口。因此,可以在RFDC之间传输大量数据。从IP Integrator可以配置RFDC IP核。

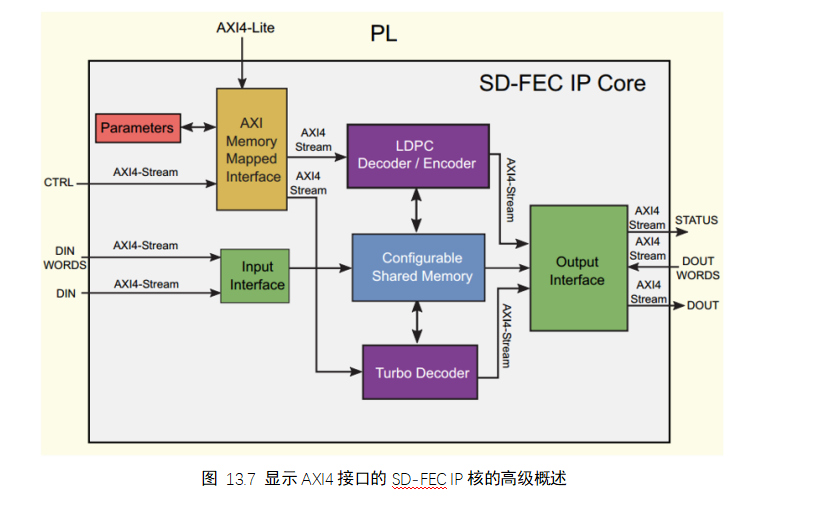

2. SD-FEC IP核

图13.7提供了SD-FEC核的概述,并显示了它与PL之间的连接。AXI4-Lite总线连接到PS,用于提供LDPC代码定义等参数,这些参数可以通过软件驱动程序进行控制。可以使用AXI4-Lite总线加载多种代码类型,然后在运行时,可以使用AXI4-Stream接口从加载的类型中选择特定的代码。AXI4-Stream接口还用于输入和输出数据,其维度是可参数化的。

精彩文章,请关注订阅号:威视锐科技