目录

一、概述

1.1 实验目的

1.2 实验背景

二、全加器设计流程

2.1 新建工程

2.2 原理图设计

四位全加器工作原理

2.3 代码设计

2.4 编译与仿真

2.5 硬件下载与演示

三、3-8译码器设计与八段数码管演示

3-8译码器

数码管

3.1 新建工程

3.2 编译与仿真

3.2.1、Verilog编程

Verilog编程实现3-8译码器

数码管驱动模块(将译码器输出的独热码转换为供应及数码管段码)

顶层模块(集成译码器与数码管驱动,连接译码器与数码管驱动模块,输入信号直接映射到数码管输出)

3.2.2、仿真

四、总结

一、概述

1.1 实验目的

1、在DE2-115开发板上,完成4位全加器系统的设计、下载和功能演示,并在FPGA上实现1位全加器;

2、完成3-8译码器的设计、下载和功能演示(利用板上的8段数码管)

1.2 实验背景

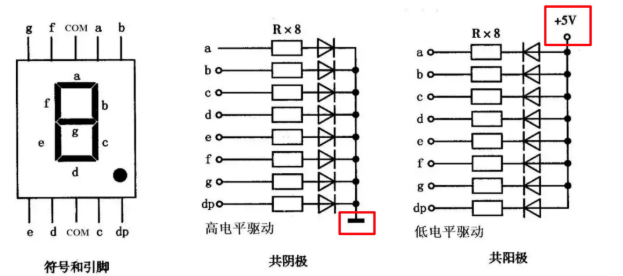

1、开发环境:Quartus Prime Lite-Edition和Modelsim SE-64 2020.4

2、开发板:DE2-115

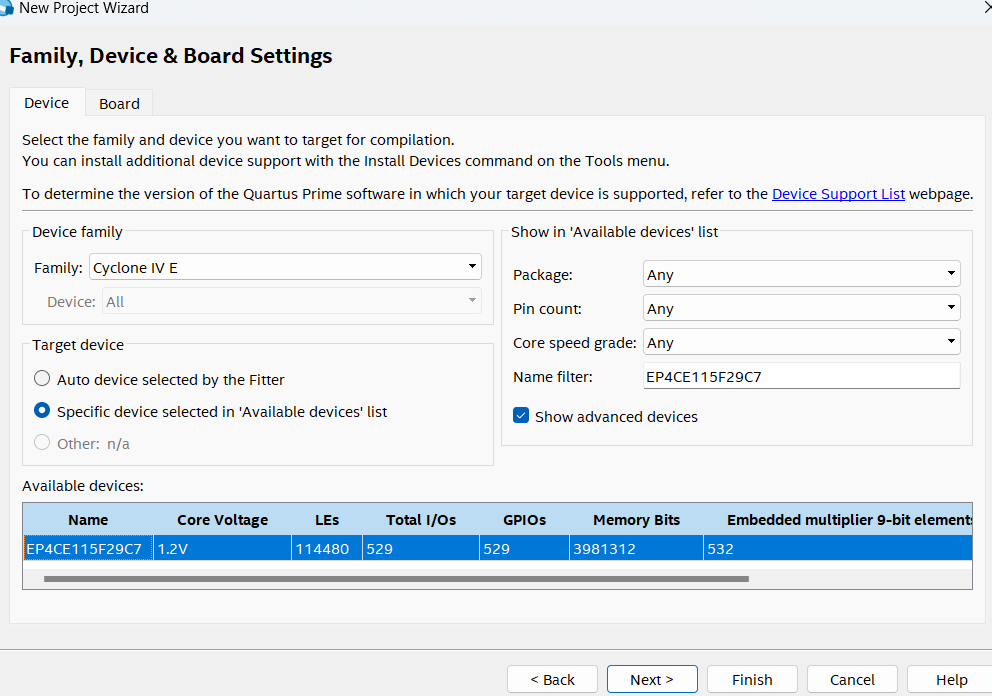

3、目标芯片:Cyclone IV EP4CE11529C7

二、全加器设计流程

2.1 新建工程

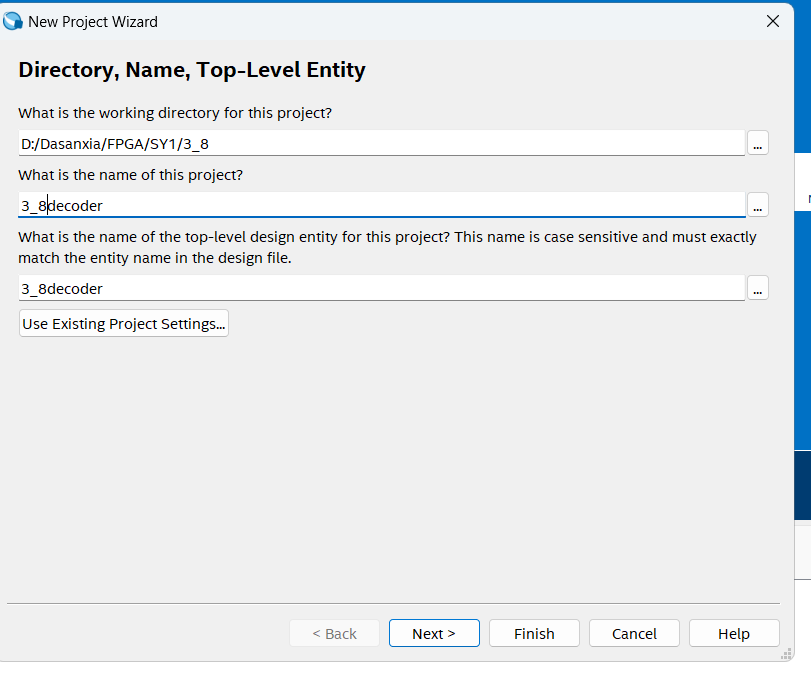

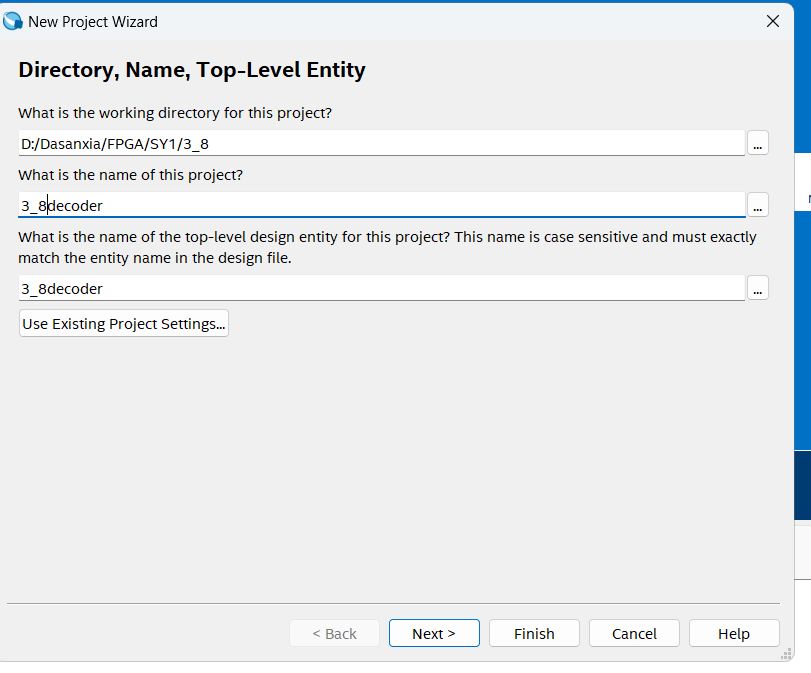

新建工程,点击New Project Wizard

为工程项目选择路径,并命名

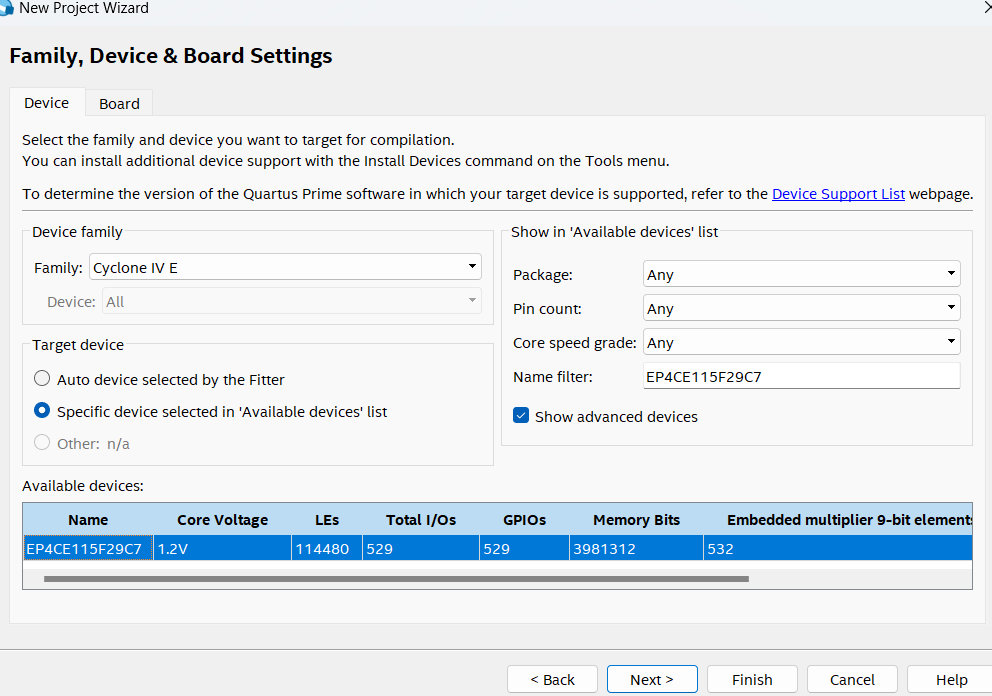

选择Cyclone IV E 的EPCE15F29C7芯片

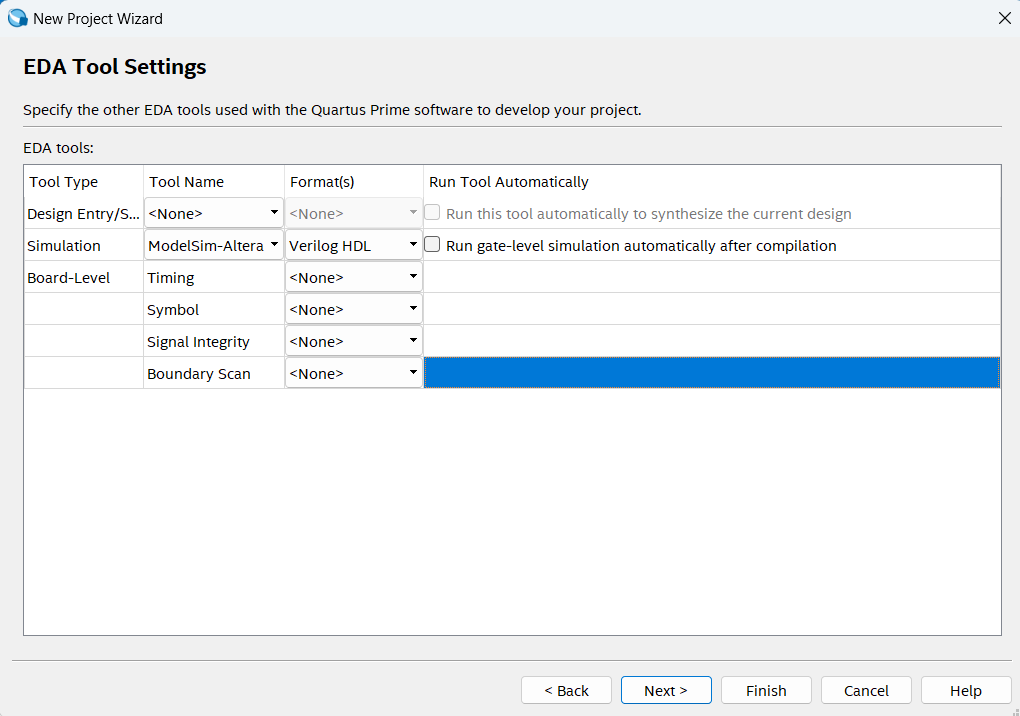

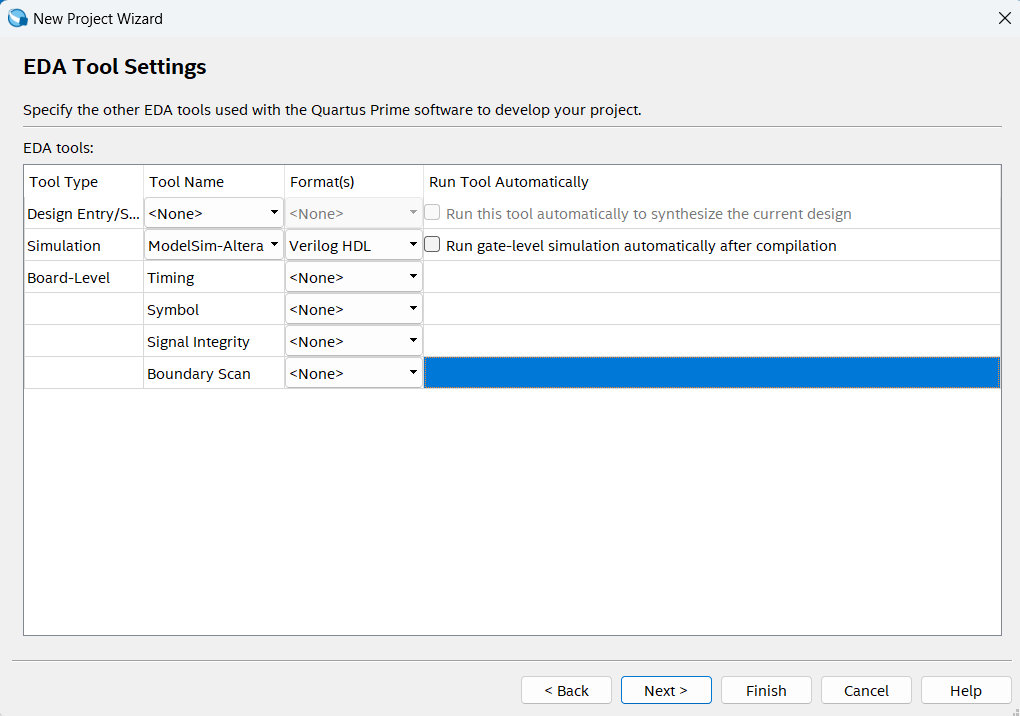

选择Modelsim-Altera进行仿真

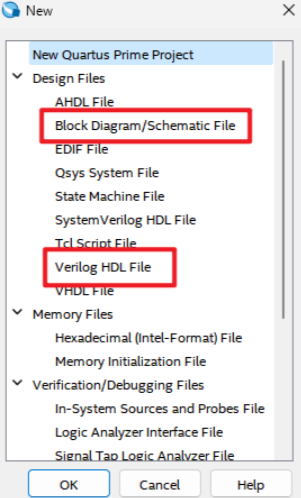

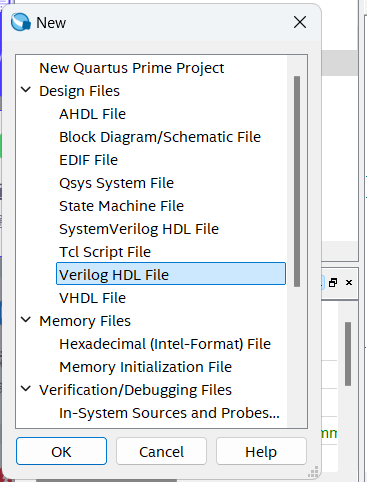

新工程项目创建完成,开始创建项目文件(File-->New-->在弹出的弹窗中选择Block Diagram/Schematic File绘制原理图)

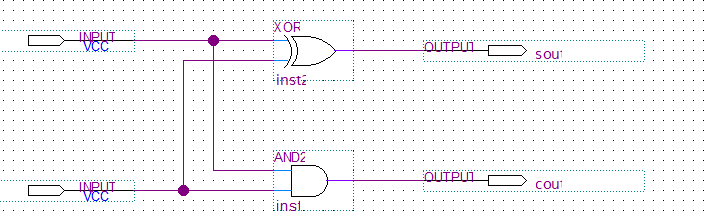

2.2 原理图设计

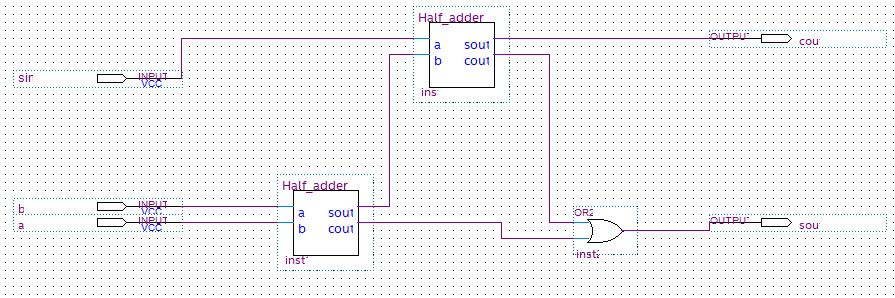

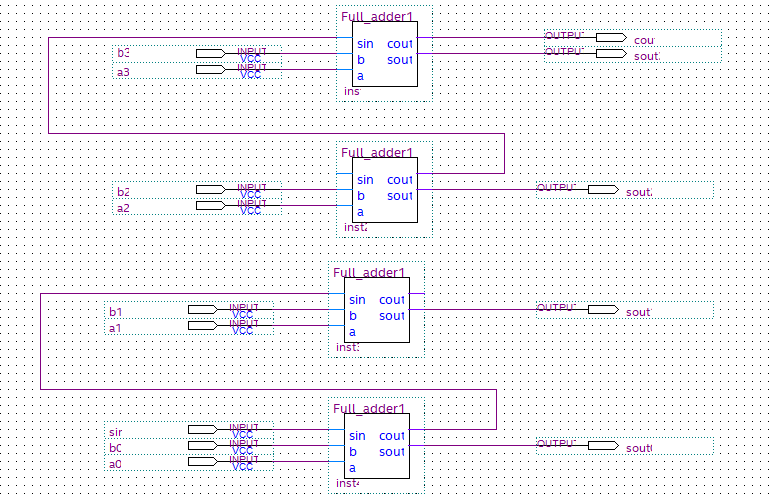

四位全加器工作原理

四位全加器接收两组四位二进制数作为输入,每组包括四个比特,除此之外还有一个初始进位输入信号(cin);全加器内部由四个全加器单元级联而成,每个全加器单元负责处理一个比特的加法运算,每个全加器单元接收三个输入信号:两个比特位输入和一个进位输入;半加器 Half_adder在每个全加器单元中,输入的两个比特位和进位信号通过特定的逻辑运算相加,加法运算的结果包括两个部分:和输出和新的进位输出,和输出是当前比特位的加法结果,而进位输出则指示加法运算中是否产生了进位;四位全加器的最终输出包括四个和输出,共同构成四位二进制数的和,此外,还有一个最终的进位输出,表示整个加法运算中是否产生了进位。

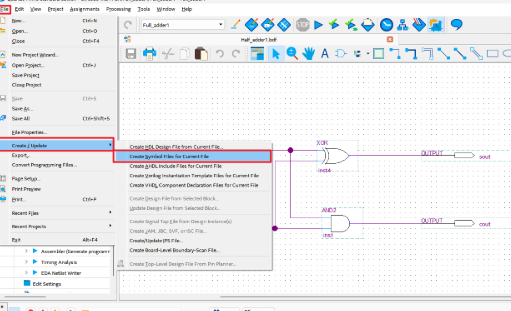

我们可以将上面的半加器进行封装,为后面全加器的设计调用(File-->Create/Update-->Create Symbol Files For Current File ),原理图文件保存类型为.dbf,封装好的元器件保存类型为.bsf

一位全加器

四位全加器

2.3 代码设计

创建代码文件进行Verilog语言编程(File-->New-->在弹出的弹窗中选择Verilog HDL File)

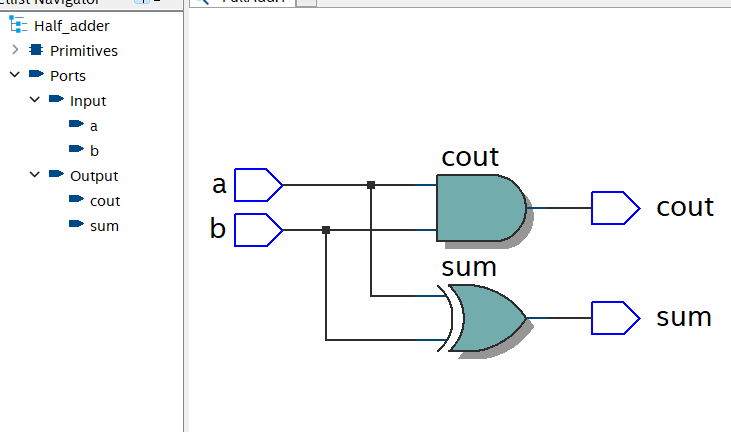

半加器

module Half_adder

(input a,b,output cout,sum

);

assign sum = a^b;

assign cout = a&b;

endmodule一位全加器

module Full_adder1

(input a,b,output sum,output cout,input sin,

);

assign{cout,sum} = a+b+sin;

endmodule四位全加器

module Full_adder4

(input [3:0] a,input [3:0] b,input sin,output [3:0] sum,output cout

);

assign{cout,sum} = a+b+sin;

endmodule2.4 编译与仿真

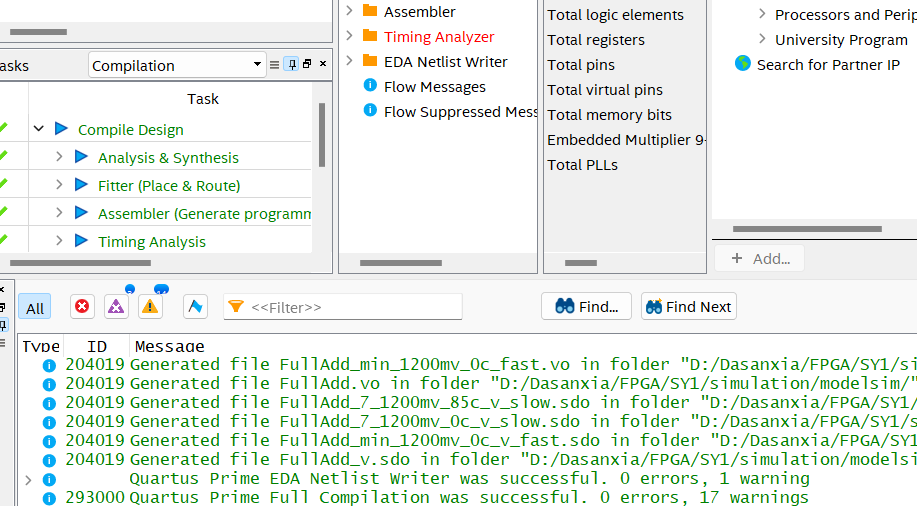

设计编写完成后对各个文件进行编译

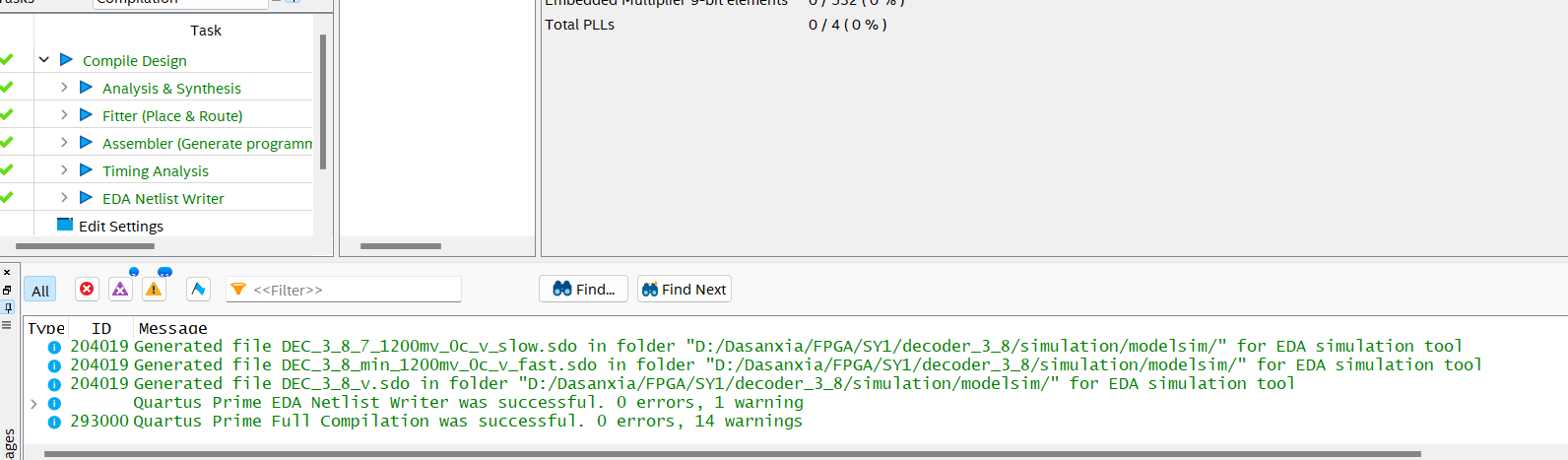

如上图(全部显示绿色)即为编译成功

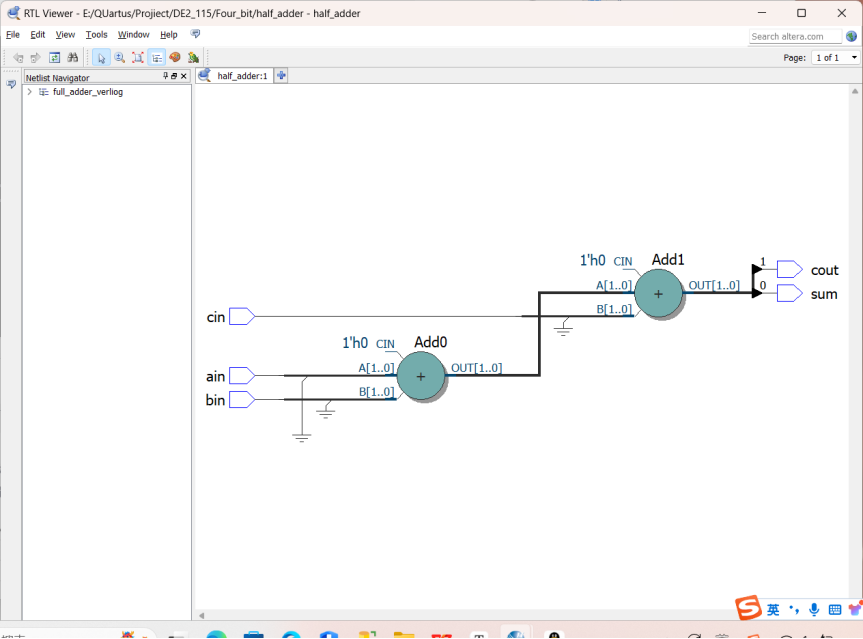

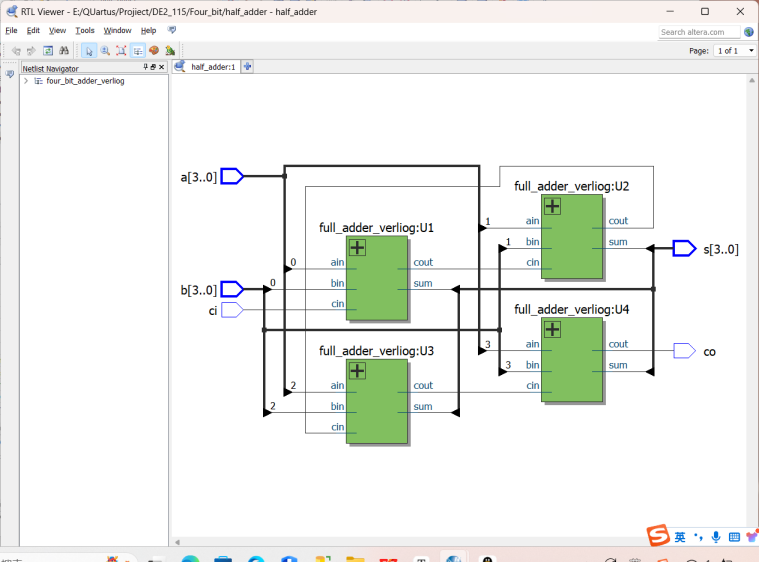

编译完成后我们可以先点击(Tool-->Netlist Viewers-->RTL Viewer)生成对应的电路图

半加器

一位全加器

四位全加器

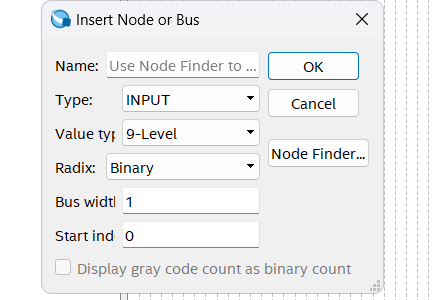

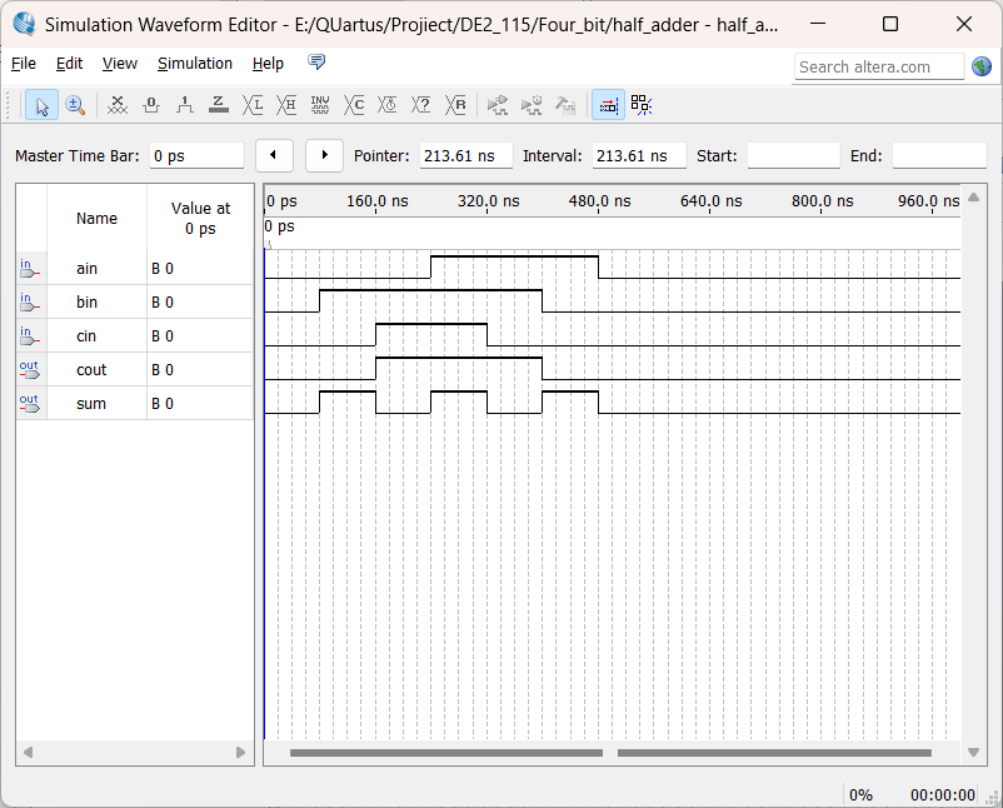

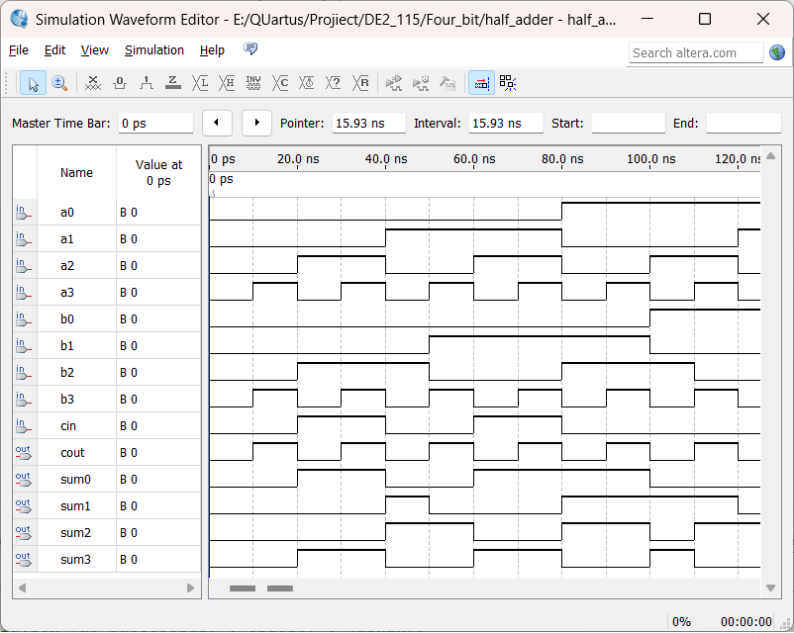

编译完成后,需要添加波形文件(File-->New-->University Program VWF),在弹出的窗口中,双击空白部分添加波形文件

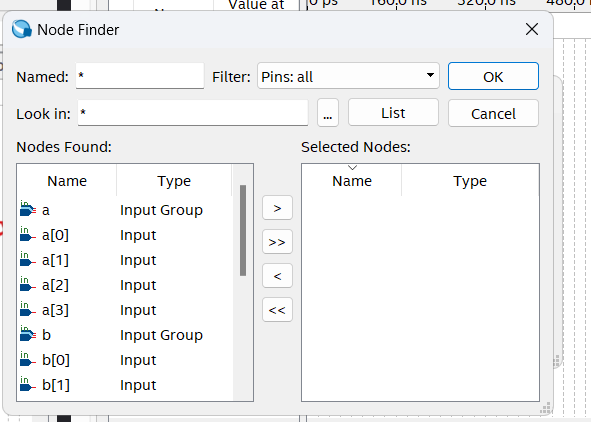

选择Node Finder...

选择List,在显示的信号列表中,选中相关信号并添加到输出列表

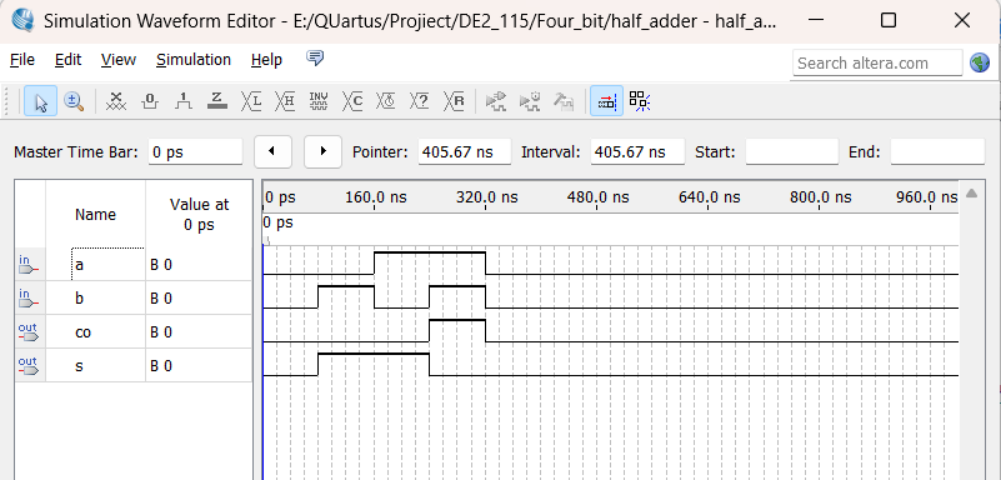

编辑输入信号

仿真结果如下

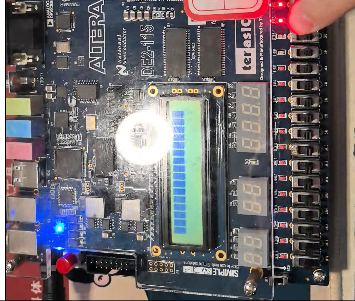

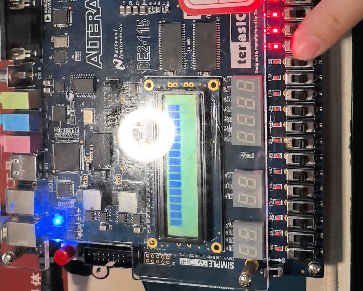

2.5 硬件下载与演示

三、3-8译码器设计与八段数码管演示

3-8译码器

3-8译码器有三个输入端(a,b,c)和八个输出端(cout[0]~cout[7]),输入端的三个二进制数可以表示从0到7的八个状态。对于每一个输入的组合,译码器只能激活一个输出线。

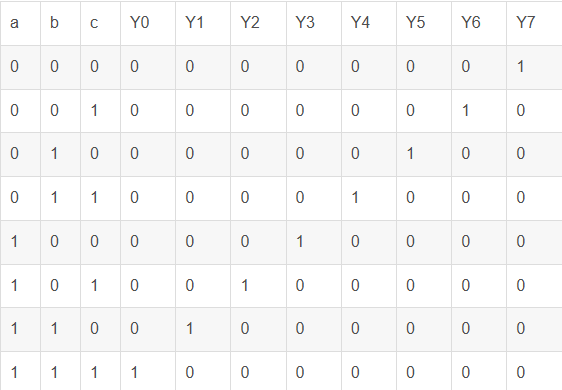

3-8译码器逻辑真值表

数码管

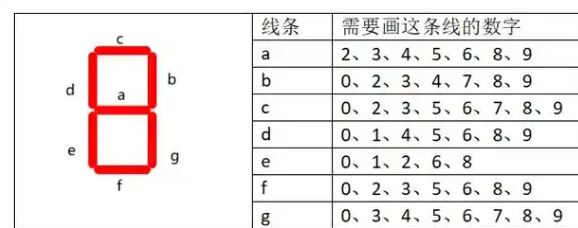

数码管按段可以分为七段数码管和八段数码管,区别就是八段数码管多了个小数点。常见的数码管有两种:共阴数码管和共阳数码管,共阴数码管就是高电平亮,低电平灭;共阳数码管就是低电平亮,高电平灭。

七段数码管

八段数码管

一个八段数码管由a,b,c,d,e,f,g,dp八个二极管组成,如上图所示,要使数码管显示不同的数字,只需点亮对应的LED即可。如:数码管显示“0”,则a,b,c,d,e,f六个LED亮,g,dp这两个LED灭,即可显示“0”。

将3-8译码器的输出连接到八段数码管的各个段上,具体来说,可以将译码器输出Y0到Y6分别连接到数码管的a到g段,Y7可以用来控制小数点dp。通过改变3-8译码器的输入,选择性的点亮数码管的某些段,从而显示出所需要的数字。

3.1 新建工程

工程创建与加法器的创建过程相同,只需对相关文件名称进行编辑即可

3.2 编译与仿真

3.2.1、Verilog编程

Verilog编程实现3-8译码器

module DEC_3to8 (input [2:0] A, // 输入3位二进制信号output reg [7:0] Y // 输出8位独热码(低电平有效)

);

always @(*) begincase (A)3'b000: Y = 8'b11111110; // Y0激活,显示03'b001: Y = 8'b11111101; // Y1激活,显示13'b010: Y = 8'b11111011; // Y2激活,显示23'b011: Y = 8'b11110111; // Y3激活,显示33'b100: Y = 8'b11101111; // Y4激活,显示43'b101: Y = 8'b11011111; // Y5激活,显示53'b110: Y = 8'b10111111; // Y6激活,显示63'b111: Y = 8'b01111111; // Y7激活,显示7default: Y = 8'b11111111; // 默认全灭endcase

end

endmodule编译代码(下面图中的内容全部变为绿色即可)

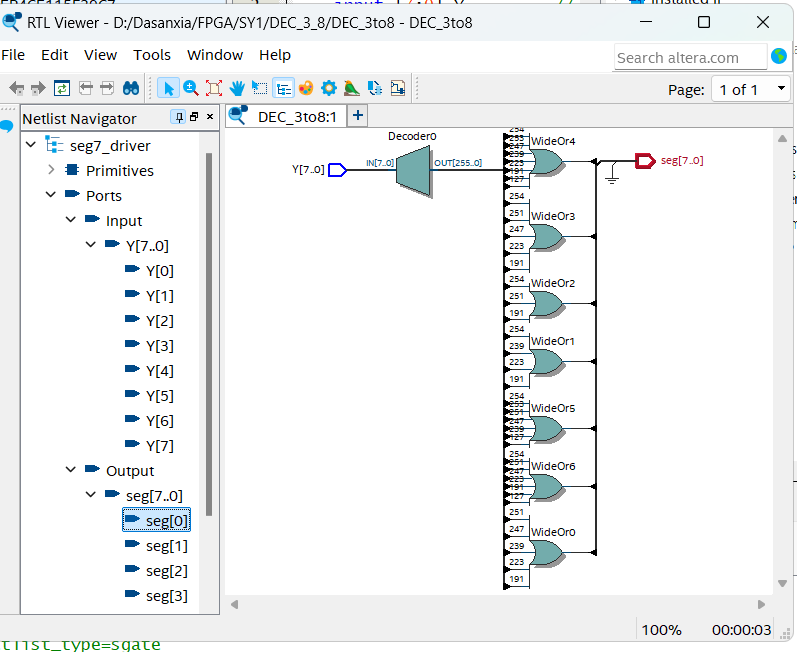

生成RTL电路(点击Tool-->Netlist Viewers-->RTL Viewer )

数码管驱动模块(将译码器输出的独热码转换为供应及数码管段码)

module seg7_driver (input [7:0] Y, // 译码器输出(独热码)output reg [7:0] seg // 数码管段码(a-g+dp)

);

always @(*) begincase (Y)8'b11111110: seg = 8'h3F; // 显示0(段码:0x3F)8'b11111101: seg = 8'h06; // 显示1(段码:0x06)8'b11111011: seg = 8'h5B; // 显示2(段码:0x5B)8'b11110111: seg = 8'h4F; // 显示3(段码:0x4F)8'b11101111: seg = 8'h66; // 显示4(段码:0x66)8'b11011111: seg = 8'h6D; // 显示5(段码:0x6D)8'b10111111: seg = 8'h7D; // 显示6(段码:0x7D)8'b01111111: seg = 8'h07; // 显示7(段码:0x07)default: seg = 8'h00; // 全灭endcase

end

endmodule

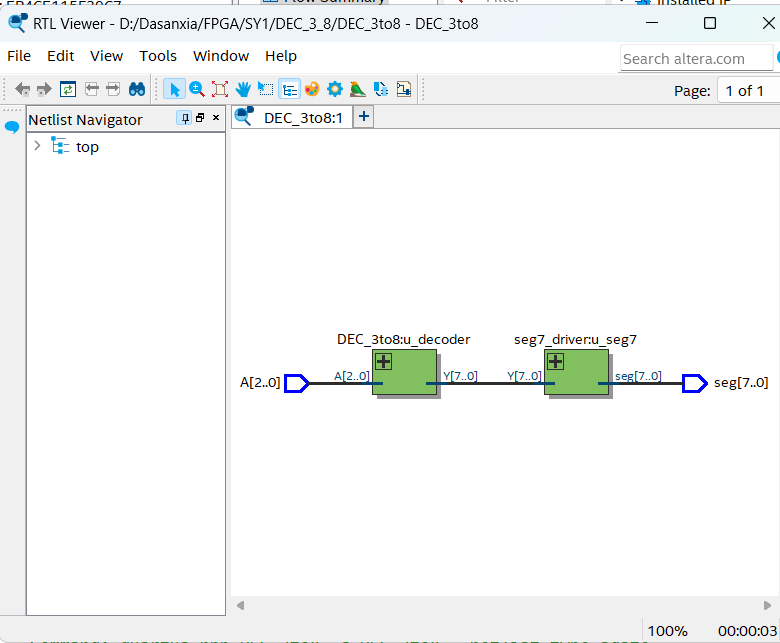

顶层模块(集成译码器与数码管驱动,连接译码器与数码管驱动模块,输入信号直接映射到数码管输出)

module top (input [2:0] A, // 拨码开关输入output [7:0] seg // 数码管段选信号

);

wire [7:0] Y; // 内部连接信号

decoder_3to8 u_decoder ( .A(A), .Y(Y) ); // 实例化译码器

seg7_driver u_seg7 ( .Y(Y), .seg(seg) ); // 实例化数码管驱动

endmodule

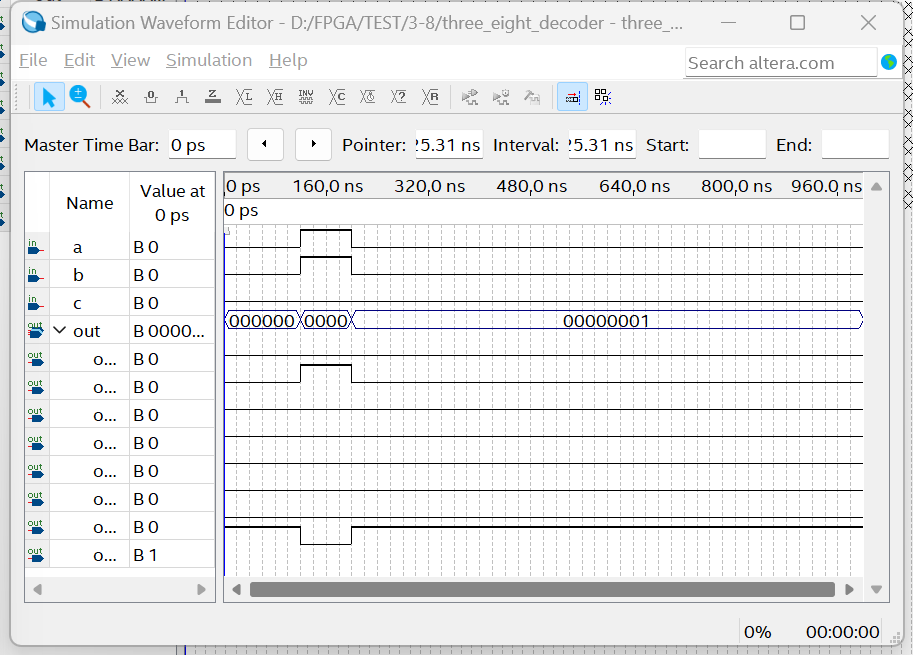

3.2.2、仿真

四、总结

本次实验在组合逻辑电路的基础上,运用Verilog编程实现了四位全加器和3-8译码器的设计,同时实现了在DE2-115开发板上的下载和功能演示。整个过程加深了我对电路设计和Verilog编程的理解,同时也锻炼了解决问题的能力。